- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

EIM write and read Turn around time Issue

Hello,

We use EIM to write and read a SRAM in asynchronous mode ,where i could able to read and write with the configuration below in IMX6Q.

EIM_CS0GCR1 = 0x00010081

EIM_CS0GCR2 = 0x00000000

EIM_CS0RCR1 = 0x04000000

EIM_CS0RCR2 = 0x00000000

EIM_CS0WCR1= 0x04000000

EIM_CS0WCR2= 0x00000000

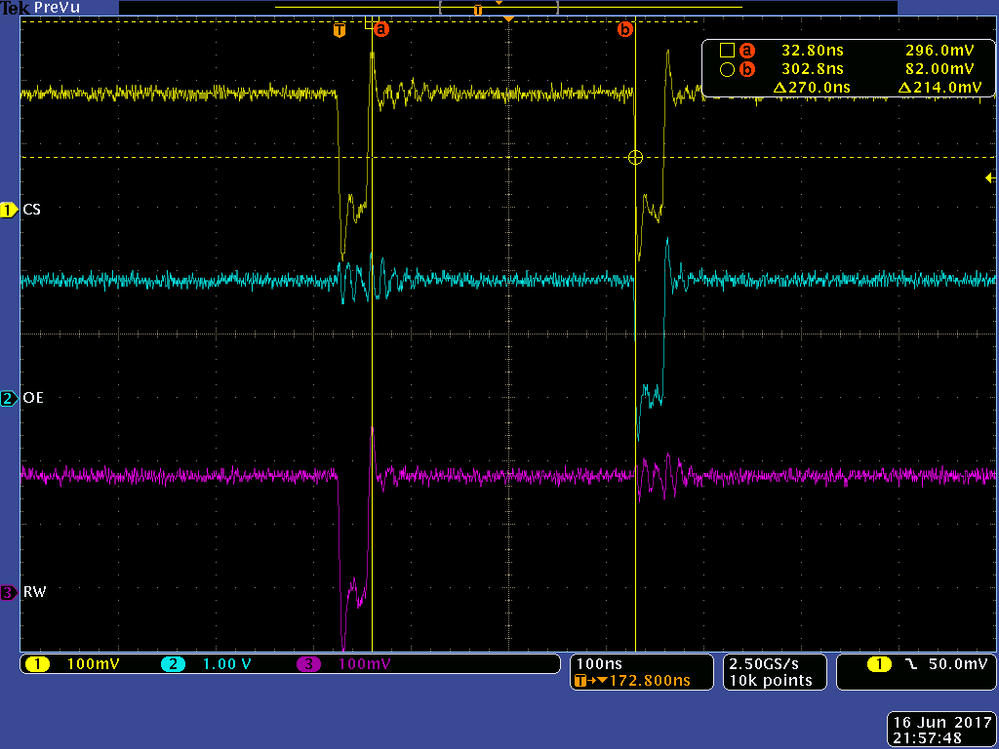

where read and write able to do in 30 ns and the turn around time in between is 270 ns.

1. I need to reduce the turn around time less than 40 ns could it be acheivable ?

2. where I need to change the configuration and things to taken care to acheive write and read with turn around time less than 100 ns?

thanks in advance ..

uday

Your current EIM setup already implements the fastest turnaround time of the accesses. So, most likely, the large gaps between the accesses are caused by the processor's internal buses arbitration timings and cannot be improved.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Artur,

Is this turnaround time coming into play when performing a because Udaya seems to be doing alternate Write and Read?

What if I am doing consecutive Writes? I am facing a similar issue, I am using a 16 bit multiplexed Asynchronous mode. And from my code I am writing 32 bytes of data in a for loop. I am using iMX51 though but I guess the symptom is the same. Here is my WEIM CS0 configuration:

{

0x00010039 , //CSxGCR1

0x00000002 , //CSxGCR2

0x20475230 , //CSxRCR1

0x00000000 , //CSxRCR2

0x609C0E98 , //CSxWCR1

0x00000000 , //CSxWCR2

}

I am able to increase/decrease the CS timing using CS0WCR1.WWSC but the delay in between two consecutive chip selects is of the order of 200nanoSecs, even though I have set CS0GCR1.CSREC to 0.

The rate at which I can send data out on the WEIM Bus is very critical, can you please suggest me a way in which the inter-CS time can be brought down? Is Burst mode synchronous access going to result in faster data throughput?