- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Dependency of tCL and tCWL values on custom hardware performance ?

Dependency of tCL and tCWL values on custom hardware performance ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Dependency of tCL and tCWL values on custom hardware performance ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

Yuri

My custom hardware is based on i.MX6Q processor and 800MHz Alliance DDR3 memory AS4C256M16D3A-12BCN.Design is most related to Nitrogen6_max design.

I set tCL = 6 and tCWL = 8 for the calibration and ddr init script. Some boards are working for this values and for some boards I had to change tCWL = 7 for better performance. Otherwise getting segmentation faults.

1) How this could happen with the same ddr layout and same production line boards ? What can we figure with this fine tuning of tCL and tCWL value of board to board ?

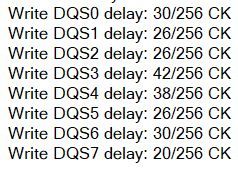

A well as I could see following write DQS delays for my boards. You can see DQS 3 and DQS 4 are way off. It should be lover than 1/8 according to NXP user manual.

2) What can we say from following DQS results ? Is it a impedance problem of those byte lanes ?

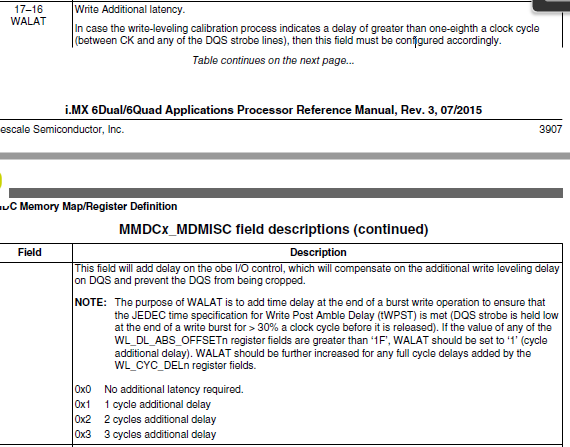

3) To optimize above values I used following method. But I couldn't see any impact for DQS 3 and DQS 4 with WALAT changes. Why is that ?

4) What are the other dependency which we can tolerate like tCWL and tCL for the memory performance ?

Here I have attached DDR3 memory data sheet and NXP calibration tool results.

I must be thankful to you if you will kindly reply me soon.

Regards,

Peter.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Look at my comments below.

I.

From practical point of view - it makes sense to modify / setup some MMDC registers

in initialization script after memory calibration, using its results. In Your case:

MMDC registers updated from calibration

Write leveling calibration

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x0018001E

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x0028001A

MMDC_MPWLDECTRL0 ch1 (0x021b480c) = 0x001A0025

MMDC_MPWLDECTRL1 ch1 (0x021b4810) = 0x0014001E

Read DQS Gating calibration

MPDGCTRL0 PHY0 (0x021b083c) = 0x02580258

MPDGCTRL1 PHY0 (0x021b0840) = 0x024C0250

MPDGCTRL0 PHY1 (0x021b483c) = 0x02600268

MPDGCTRL1 PHY1 (0x021b4840) = 0x02500230

Read calibration

MPRDDLCTL PHY0 (0x021b0848) = 0x423A3A3C

MPRDDLCTL PHY1 (0x021b4848) = 0x3A383842

Write calibration

MPWRDLCTL PHY0 (0x021b0850) = 0x3A3A403C

MPWRDLCTL PHY1 (0x021b4850) = 0x403A403A

If overnight test with new initialization parameters is OK - the found parameters are good

candidates for final release.

II.

tCL and tCWL should be the same for i.MX6 MMDC and DDR3 (AS4C256M16D3A).

III.

Please verify PCB design, using Excel page named “MX6 DRAM Bus Length Check” in “HW Design

Checking List for i.Mx6”.

https://community.nxp.com/docs/DOC-93819

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer

button. Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter

unfortunately I am not aware of nxp documentation for optimization tCL and tCWL memory settings.

I believe such documentation should be provided by memory vendors.

NXP i.MX6 DDR Script Aid suggest to enter tCL and tCWL from datasheet mamories, without changes.

>>4) What are the other dependency which we can tolerate like tCWL and tCL for the memory performance ?

suggest to post this to memory vendor (Alliance) tech support

WALAT is described on p.18 AN4467 i.MX 6 Series DDR Calibration

https://www.nxp.com/docs/en/application-note/AN4467.pdf

In general issues with improving performance and customer boards analysis may be provided with

extended support of Professional Services

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------