- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

DDR training FAILED on i.mx8MQ uboot 2018.03-00008-g7ade5b4

Hello,

I'm trying to update a project that uses u-boot 2017.03-imx_v2017.03_4.9.88_2.0.0_ga

to the new release of u-boot (2018.03-00008-g7ade5b4).

The board is running fine with the old u-boot version.

We inserted the RAM data in to this excel file:

Than we performed the tests with i.MX8 MSCALE SERIES DDR Tool Release (V2.10) and the RAM calibration seems correct:

*************************************************************************

MX8 DDR Stress Test V2.10

Built on Mar 5 2019 14:26:42

*************************************************************************--Set up the MMU and enable I and D cache--

- This is the Cortex-A53 core

- Check if I cache is enabled

- Enabling I cache since it was disabled

- Push base address of TTB to TTBR0_EL3

- Config TCR_EL3

- Config MAIR_EL3

- Enable MMU

- Data Cache has been enabled

- Check system memory register, only for debug- VMCR Check:

- ttbr0_el3: 0x91d000

- tcr_el3: 0x2051c

- mair_el3: 0x774400

- sctlr_el3: 0xc01815

- id_aa64mmfr0_el1: 0x1122- MMU and cache setup complete

*************************************************************************

ARM clock(CA53) rate: 800MHz

DDR Clock: 1600MHz============================================

DDR configuration

DDR type is LPDDR4

Data width: 32, bank num: 8

Row size: 16, col size: 10

One chip select is used

Number of DDR controllers used on the SoC: 1

Density per chip select: 2048MB

Density per controller is: 2048MB

Total density detected on the board is: 2048MB

============================================MX8M: Cortex-A53 is found

*************************************************************************

============ Step 1: DDRPHY Training... ============

---DDR 1D-Training @1600Mhz...

[Process] End of CA training

[Process] End of initialization

[Process] End of read enable training

[Process] End of fine write leveling

[Process] End of read DQ deskew training

[Process] End of MPR read delay center optimization

[Process] End of Write Leveling coarse delay

[Process] End of write delay center optimization

[Process] End of read delay center optimization

[Process] End of max read latency training

[Result] PASS

---DDR 1D-Training @334Mhz...

[Process] End of CA training

[Process] End of initialization

[Process] End of read enable training

[Process] End of fine write leveling

[Process] End of MPR read delay center optimization

[Process] End of Write Leveling coarse delay

[Process] End of write delay center optimization

[Process] End of read delay center optimization

[Process] End of max read latency training

[Result] PASS

---DDR 2D-Training @1600Mhz...

[Process] End of initialization

[Process] End of 2D read delay/voltage center optimization

[Process] End of 2D read delay/voltage center optimization

[Process] End of 2D write delay/voltage center optimization

[Process] End of 2D write delay/voltage center optimization

[Result] PASS============ Step 2: DDR memory accessing... ============

....[Result] OK============ Step 3: DDR parameters processing... ============

[Result] DoneSuccess: DDR Calibration completed!!!

'ddr_init.c' is created!

'ddrphy_train.c' is created!

'lpddr4_timing.c' is created!

'lpddr4_timing.c' is created!

With the same tool we than generated the lpddr4_timing.c file and copied into uboot.

When we start to boot the device with uuu, we get the "Training FAILED" error:

U-Boot SPL 2018.03-00008-g7ade5b4-dirty (May 13 2019 - 15:42:59 +0000)

PMIC: PFUZE100 ID=0x10

DDRINFO: start lpddr4 ddr init

DRAM PHY training for 3200MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training FAILED

DRAM PHY training for 667MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training FAILED

DRAM PHY training for 3200MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training FAILED

DDRINFO:ddrphy calibration done

DDRINFO: ddrmix config done

Normal Boot

Trying to boot from USB SDP

"Synchronous Abort" handler, esr 0x96000000

elr: 00000000007e58a0 lr : 00000000007e57f8

x0 : 0000f8044220f804 x1 : 0000f8040000f7d5

x2 : 0000000042200010 x3 : 00000000007fbcb0

x4 : 00000000007fbca0 x5 : 00000000000f0048

x6 : 0000000000000002 x7 : 0000000000185e38

x8 : 0000000000185c40 x9 : 0000000000000001

x10: 00000000ffffffd0 x11: 0000000000000006

x12: 000000000001869f x13: 0000000000000200

x14: 0000000000000038 x15: 00000000ffffffff

x16: 0000000000000000 x17: 0000000000000000

x18: 0000000000185e40 x19: 0000000000000030

x20: 0000000000000040 x21: 0000000042200030

x22: 0000000000000390 x23: 0000000000000387

x24: 00000000007f3497 x25: 00000000007fc000

x26: 00000000deadbeef x27: 0000000000000000

x28: 00000000000000f0 x29: 0000000000185cc0

Resetting CPU ...

resetting ...

Any suggestion on what is happening? The board is perfectly working with an old version of u-boot.

Hi Francesco

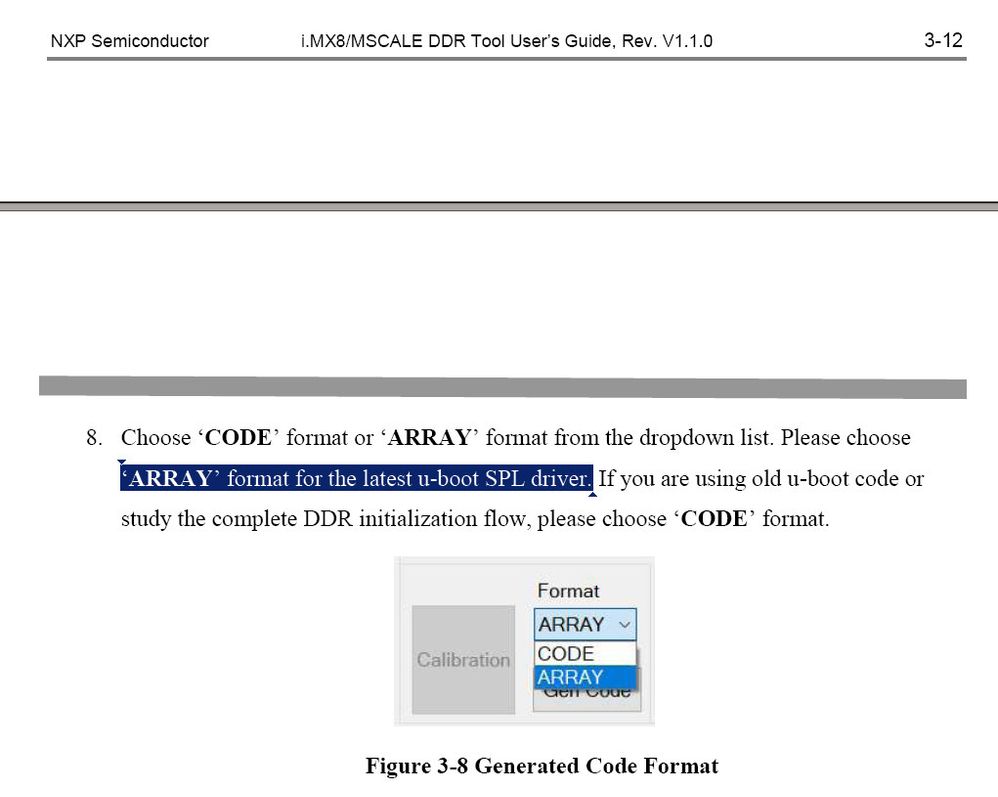

one can check that ‘ARRAY’ format was use as in below part of MSCALE_DDR_Tool_User_Guide.pdf

lpddr4_timing_b0.c\imx8mq_evk\freescale\board - uboot-imx - i.MX U-Boot

and test uboot just booting from sd as described in sect.4.3.4 Copying a bootloader

image attached Linux Guide.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Igor,

Thank you for your reply.

Yes, we already used the correct 'ARRAY' format (with the other format, we cannot even compile u-boot).

Unfortunately we cannot boot from SD card because the board has only an eMMC. We can add an SD by soldering some wires but we need some time, will try this tomorrow and see what happens.

Thank you,

Regards

Francesco

Ok, I managed to re-flash the eMMC with the new u-boot, the result is the same:

U-Boot SPL 2018.03-00008-g7ade5b4-dirty (May 13 2019 - 15:42:59 +0000)

PMIC: PFUZE100 ID=0x10

DDRINFO: start lpddr4 ddr init

DRAM PHY training for 3200MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training FAILED

DRAM PHY training for 667MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training FAILED

DRAM PHY training for 3200MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training FAILED

DDRINFO:ddrphy calibration done

DDRINFO: ddrmix config done

Normal Boot

Trying to boot from MMC1

reason may be in firmware versions, one can recheck that ddr tool and used uboot

use the same versions, details are given in sect.4.3 Building u-boot image

MSCALE_DDR_Tool_User_Guide.pdf included in i.MX8 MSCALE SERIES DDR Tool Release (V2.10)

Best regards

igor