- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: DDR TOOL hangs with iMX8MM board

DDR TOOL hangs with iMX8MM board

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi support,

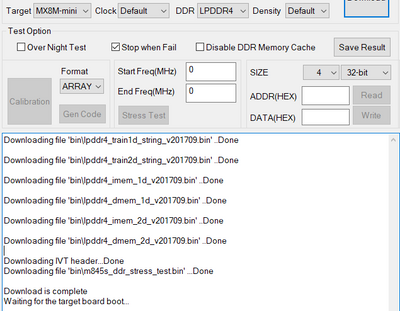

I am developping a iMX8mm board, when I run the ddr tool V3.20, it hangs below.

My PMIC is PCA9450AHN, and the uart configuration is correct.

How can I debug it?

Thanks.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi everyone,

This issue is fixed, there is something wrong with our hardware design, which makes the CPU enter TEST MODE.

Many thanks to all your support.

Best wishes.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I also measured the uart2 tx, rx pin, there are no signals on them.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, I just follow the spl pmic setting for PCA9450, but it still hangs there, I will measure the PCA9450 signal. Another question, should I change the ddr firmware in the ddr test tool as below?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The pmic pca9450, the otp setttings already can work for LPDDR4.

Here is the demo, change the uart to uart3.

The board is i.MX8MM pca9450 evk.

Please make sure you connect the TX to RX and RX to TX for those two sides.

--- mscale_ddr_tool _v3.20\script\mx8mm\mx8mm_micron_lpddr4_2gb_2d_1500m_200m_50m_32bit_1cs_RPAv16.ds.orig

+++ mscale_ddr_tool _v3.20\script\mx8mm\mx8mm_micron_lpddr4_2gb_2d_1500m_200m_50m_32bit_1cs_RPAv16_uart3.ds

@@ -16,12 +16,13 @@

################step 0: configure debug uart port. Assumes use of UART IO Pads. #####

##### If using non-UART pads (i.e. using other pads to mux out the UART signals), #####

##### then it is up to the user to overwrite the following IO register settings #####

-memory set 0x3033023C 32 0x00000000 #IOMUXC_SW_MUX_UART2_RXD

-memory set 0x30330240 32 0x00000000 #IOMUXC_SW_MUX_UART2_TXD

-memory set 0x303304A4 32 0x0000000E #IOMUXC_SW_PAD_UART2_RXD

-memory set 0x303304A8 32 0x0000000E #IOMUXC_SW_PAD_UART2_TXD

-memory set 0x303304FC 32 0x00000000 #IOMUXC_SW_MUX_UART2_SEL_RXD

-sysparam set debug_uart 1 #UART index from 0 ('0' = UART1, '1' = UART2, '2' = UART3, '3' = UART4)

+memory set 0x303301F4 32 0x00000001 #IOMUXC_SW_MUX_ECSPI1_SCLK

+memory set 0x303301F8 32 0x00000001 #IOMUXC_SW_MUX_ECSPI1_MOSI

+memory set 0x3033045C 32 0x0000000E #IOMUXC_SW_PAD_ECSPI1_SCLK

+memory set 0x30330460 32 0x0000000E #IOMUXC_SW_PAD_ECSPI1_MOSI

+memory set 0x30330504 32 0x00000000 #IOMUXC_SW_MUX_UART3_SEL_RXD

+

+sysparam set debug_uart 2 #UART index from 0 ('0' = UART1, '1' = UART2, '2' = UART3, '3' = UART4)

################step 1: DDR clock configuration################

memory set 0x30391000 32 0x8F00003F #SRC_DDRC_RCR_ADDR: assert [0]ddr1_preset_n, [1]ddr1_core_reset_n, [2]ddr1_phy_reset, [3]ddr1_phy_pwrokin_n, [4]src_system_rst_b!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks. Do I need to flash the spl,uboot,kernel to the boot device before running ddr tool?