- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: Can i.MX8M mini use DDR3?

Can i.MX8M mini use DDR3?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Can i.MX8M mini use DDR3?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I purchased i.MX8M mini EVK

The EVK I purchased has 2GB of LPDDR4 designed.

(There are also EVKs designed with DDR4)

Can I change to DDR3?

Can I design with 512MB or 1GB?

The product I am designing now does not have much work on the video side.

It is about checking the video seamlessly by connecting HD-class CAM with USB.

Please review

Thank you

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Danny,

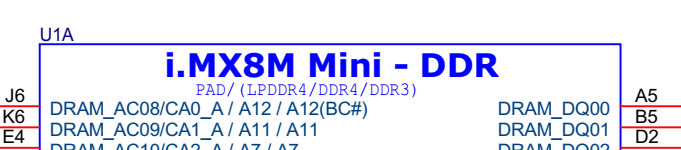

i.MX8 Mini supports 32/16-bit LPDDR4 (up to 1.5 GHz), DDR4-2400, and DDR3L-1600. It also supports up to 8 Gbyte DDR memory space.

Regards,

Mrudang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mrudang

DDRL can be used. Can I modify it by referring to the DDR4 design?

Please share any information I can refer to.

And is there no problem with 1GB or 512MB other than 2GB?

Thank you

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Danny,

Yes DDR3L can be used. And there is no issue with 1GB or 512MB.

Kindly share your schematic once you are done with the interfacing.

Mrudang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Danny,

Please refer to IMX8MMHDG: i.MX 8M Mini Hardware Developer’s Guide for DDR3L.

- Refer complete sec 3.4 DDR design recommendations for pin signal assignment, signal swapping etc.

- Also, refer to reference schematic pg. no 5 of SCH-35104 for DDR3L interface and net swapping based on signal routing.

- eMMC interface looks good. (Reference pg. no 9 of SCH-31399 C2)

Regards,

Mrudang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mrudang

I will refer to IMX8MMHDG: i.MX 8M Mini Hardware Developer’s Guide

But I have a question

Where is the circuit diagram for reference (SCH-35104, SCH-31399)?

This is not in IMX8MMHDG: i.MX 8M Mini Hardware Developer’s Guide, what document?

Is the document I know different from the document you are telling me?

Please let me know

Thank you

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mrudang

The attached file is a circuit diagram for LPDDR4 and DDR4

Is there any circuit diagram for DDR3L?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Danny,

The schematic is based on DDR4 and LPDDR4. but they have also mentioned DDR3 as well. It means this reference schematic is also applicable for DDR3 signal interface as well.

Section 3.4 of IMX8MMHDG: i.MX 8M Mini Hardware Developer’s Guide has provided pin signal assignment for all 3 DRAM.

Mrudang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mrudang

I referred to the document composed of DDR4 (SPF-35104) and prepared a circuit diagram for review. (The circuit diagram was attached)

Have you seen the circuit diagram I attached?

If you have seen it, please give me a comment on it

According to the document (IMX8MMHDG: i.MX 8M Mini Hardware Developer's Guide), when using DDR3L, it seems to use four DDR3L.

However, the circuit diagram using DDR4 uses two DDR4.

If there is a circuit diagram composed of DDR3L, please attach it.

Thanks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Danny,

Please resend me the updated schematic.

If they have used 4 DRAM for their application. If we need to use 2 DRAM based on data lines and memory density we need to connect the DQ signals and address signals.

Mrudang.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mrudang

Among the above ripples, there is a circuit diagram I attached

I want you to give me a comment on it

1. Only two DDR3Ls are used? Should I use 4?

2. Please inform the wrong part of the attached circuit diagram.

3. Please attach a reference circuit diagram written in DDR3L.

4. Is there a circuit diagram written in i.MX8MM and DDR3L?

Thank you

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Danny,

The attachment is missing.

Please share the updated one.

What do you mean by the wrong part?

Do you use Skype?

Share your id.

Mrudang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mrudang

Attached file is here

'Wrong part' is to review the circuit diagram

I'm sorry, but I don't use Skype

Is there no DDR3L circuit diagram?

Thank you

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Danny,

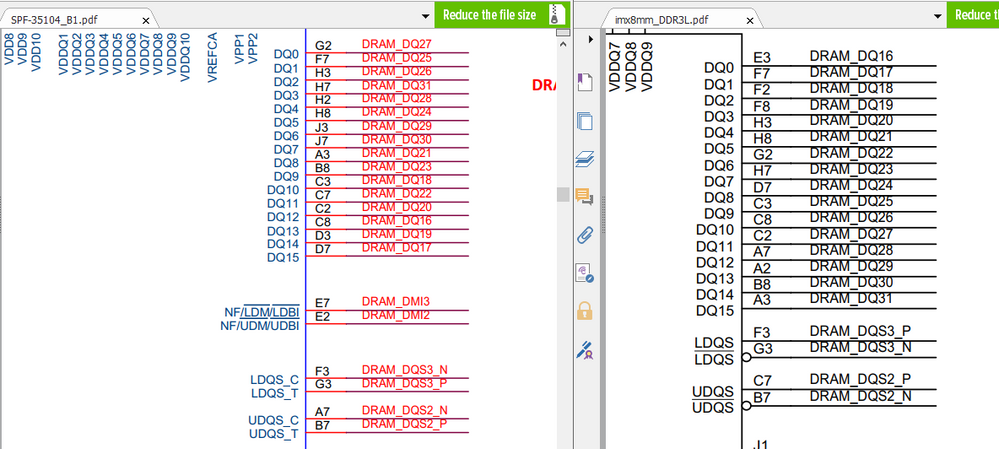

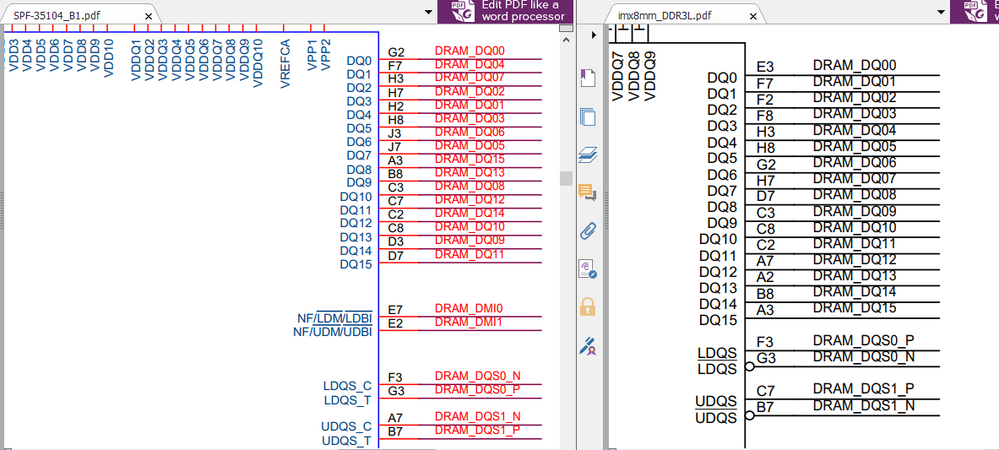

As I have informed you earlier, pls assign the data lines as shown in ref design.

Please update.

Mrudang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

HI Danny,

Now DRAM looks good. I believe Parity, Ten and ACT_n pins are not there in DDR3L. Those are for DDR4.

Is there anything else that could be a big problem besides the data line?

Ans: Data Mask, Data strobe has to be matched with Data lines. Earlier schematic it was not matching.

I think the wiring of DDR4 and DDR3L is similar, so I can do artwork by referring to the DDR4 schematic and PCB file.

Ans: Yes.

Mrudang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mrudang

I don't use it in DDR3L, but I will treat Parity, Ten and ACT-N as TP

The other part of the wiring of DDR3L is said to be okay, so I will start working as it is.

Thank you

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sure

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mrudang

i.MX8M mini is applicable to DDR3L and 512MB is also available.

Then I will design DDR3L, 1GB

I'll share it when finished, so please review

Thank you