- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Re: About MMDC PHY Read DQS Gating Control Register in i.MX6DQ.

About MMDC PHY Read DQS Gating Control Register in i.MX6DQ.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear All,

I have a question about DDR setting register.

My customer would like to use DDR3_x64.

Refer to 44.12.46 MMDC PHY Read DQS Gating Control Register 0 (MMDCx_MPDGCTRL0) in MCIMX6DQRM(Rev.2).

There is below description.

======

For Channel 0: DDR3_x16, DDR3_x32, DDR3_x64

For Channel 1: DDR3_x64

======

Next, refer to "DG_HC_DEL1" bits.

-----------

Read DQS gating half cycles delay for Byte1 (channel 0 register) and Byte5 in 64-bit mode (channel 1 register)

-----------

Last, refer to "DG_CMP_CYC" and "DG_DIS" bit ,etc.

There isn't the description of channel 0 and channel 1.

[Question]

How should one set channel 0 and channel 1 to MMDCx_MPDGCTRL0?

I couldn't understand well...

Best Regards,

Keita

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Keita,

>DG_HC_DEL1 and DG_HC_DEL0 bits were set for Channel 0 & 1 PHY?

Yes.

>Refer to Figure 2. DDR3 64-Bit Calibration Registers in AN4476(Rev.2).

>I have understood that MMDCx_MPDGCTRL0 register is "Calibration control" which is in Figure.2.

I think Figure 2 just shows generic structure, not registers.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Keita

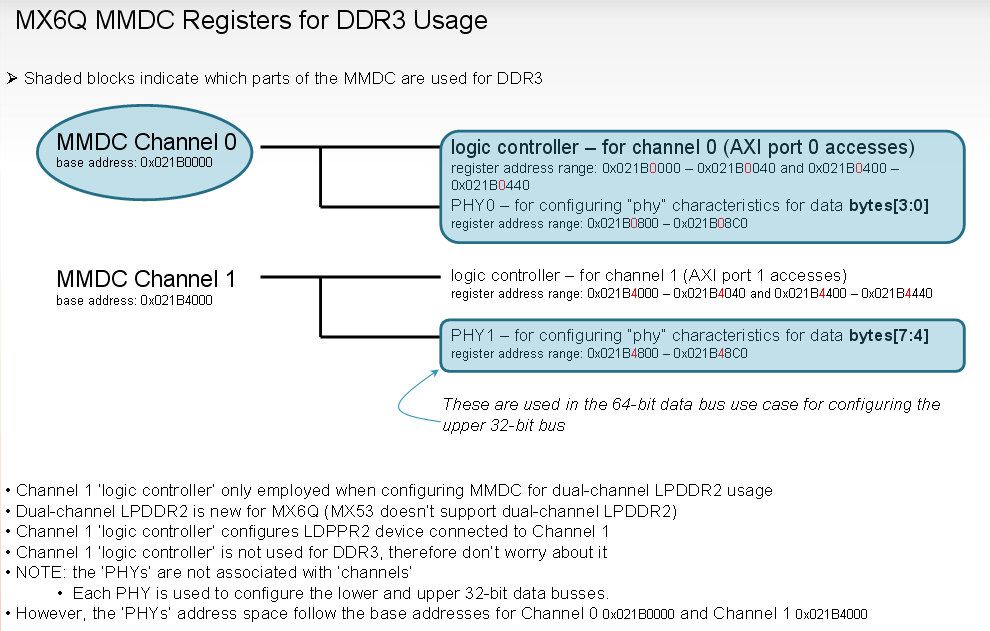

DQS Gating is used only for DDR3 memory, only channel 0 is used.

I.MX6Q has two “logic controllers” – one controller for each “channel”

or AXI port - this is not relevant for DDR3, only for LPDDR2.

Channel 1 ‘logic controller’ only employed when configuring MMDC for

dual-channel LPDDR2 usage and not used for DDR3.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thank you for your reply.

Sorry, I couldn't understand well.

Let me clarify these registers again.

My customer will use DDR3 with x64 bits width.

Refer to 44.12.46 MMDC PHY Read DQS Gating Control Register 0 (MMDCx_MPDGCTRL0) in MCIMX6DQRM(Rev.2).

Are these below description typo??

1. Supported Mode Of Operations:

======

For Channel 0: DDR3_x16, DDR3_x32, DDR3_x64

For Channel 1: DDR3_x64

======

2. DG_HC_DEL1 and DG_HC_DEL0 bits

======

Read DQS gating half cycles delay for Byte1 (channel 0 register) and Byte4 in 64-bit mode (Channel 1 register)

======

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Keita,

sorry, I couldn't understand well:

where so you think typo - what word exactly?

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

You answered; DQS Gating is used only for DDR3 memory, only channel 0 is used.

So I consider that below description looks typo.

1. Supported Mode Of Operations:

======

For Channel 0: DDR3_x16, DDR3_x32, DDR3_x64

For Channel 1: DDR3_x64

======

2. DG_HC_DEL1 and DG_HC_DEL0 bits

======

Read DQS gating half cycles delay for Byte1 (channel 0 register) and Byte4 in 64-bit mode (Channel 1 register)

======

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Keita,

thanks for clarifcation.

This is not accurate wording, since there are

two logic terms (please look at image above):

1. Channel1 logic controller

2. Channel1 PHY

meaning in text was for "Channel1 PHY" - configuration

characteristics for data bytes [4-7]

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thank you for your reply.

i.e. DG_HC_DEL1 and DG_HC_DEL0 bits were set for Channel 0 & 1 PHY?

Refer to Figure 2. DDR3 64-Bit Calibration Registers in AN4476(Rev.2).

I have understood that MMDCx_MPDGCTRL0 register is "Calibration control" which is in Figure.2.

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Keita,

>DG_HC_DEL1 and DG_HC_DEL0 bits were set for Channel 0 & 1 PHY?

Yes.

>Refer to Figure 2. DDR3 64-Bit Calibration Registers in AN4476(Rev.2).

>I have understood that MMDCx_MPDGCTRL0 register is "Calibration control" which is in Figure.2.

I think Figure 2 just shows generic structure, not registers.

Best regards

igor