- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ ナレッジベース

- :

- Patch to Support BT656 and BT1120 Output For i.MX6 BSP

Patch to Support BT656 and BT1120 Output For i.MX6 BSP

- RSS フィードを購読する

- 新着としてマーク

- 既読としてマーク

- ブックマーク

- 購読

- 印刷用ページ

- 不適切なコンテンツを報告

Patch to Support BT656 and BT1120 Output For i.MX6 BSP

Patch to Support BT656 and BT1120 Output For i.MX6 BSP

Here are two patches to support BT656 and BT1120 output for i.MX6 ipuv3. With this patch, the i.MX6 can support the CVBS output on TV encoder. It is useful for a TV box.

"L3.0.35_1.1.0_GA_bt656_output_patch.zip" is the patch for Freescale L3.0.35_1.1.0_GA_iMX6DQ BSP.

"r13.4.1_bt656_output_patch.zip" is the patch for Freescale Android R13.4.1 BSP.

1. Features supported:

1) Support BT656(8 bits) and BT1120 (16 bits)interlaced output on display port.

2) Support both RGB and YUV frame buffer for BT656/BT1120 output.

3) Support PAL and NTSC mode.

4) Support on the fly switch between PAL and NTSC mode.

5) Support CVBS output based on adv7391 TV encoder.

2. Hardware link between iMX6 and adv7391 TV encoder chip.

IPU1_DI0_DISP_CLK connected to adv7391 CLKIN pin.

IPU1_DISP0_DAT_23~DISP0_DAT_16 connected to adv7391 P7~P0 pins.

IPU1_DI0_PIN2 connected to adv7391 HSYNC pin. (option)

IPU1_DI0_PIN4 connected to adv7391 VSYNC pin. (option)

- Android R13.4.1 kernel.

3. How to use

-- Copy the two patch files to kernel folder.

$ git apply ./0001-Support-BT656-and-BT1120-output-for-iMX6-ipuv3.patch

$ git apply ./0002-Support-adv739x-TV-encoder-for-BT656-output.patch

-- Select them in kernel config and build the new kernel image:

Device Drivers --->

Graphics support --->

[*] MXC BT656 and BT1120 output

[*] ADV7390/7391 TV Output Encoder

-- Uboot parameters for video mode

Output BT656 NTSC data to display port with UVYV frame buffer mode:

"video=mxcfb0:dev=bt656,BT656-NTSC,if=BT656,fbpix=UYVY16"

Output BT656 NTSC data to display port with RGB565 frame buffer mode:

"video=mxcfb0:dev=bt656,BT656-NTSC,if=BT656,fbpix=RGB565"

Output BT656 PAL data to display port with RGB24 frame buffer mode:

"video=mxcfb0:dev=bt656,BT656-PAL,if=BT656,fbpix=RGB24"

Output CVBS NTSC signal on adv7391 with UYVY frame buffer mode:

"video=mxcfb0:dev=adv739x,BT656-NTSC,if=BT656,fbpix=UYVY16"

Output CVBS PAL signal on adv7391 with RGB565 frame buffer mode:

"video=mxcfb0:dev=adv739x,BT656-PAL,if=BT656,fbpix=RGB565"

-- Switch between PAL and NTSC

$ echo D:720x480i-60 > /sys/class/graphics/fb0/mode

$ echo D:720x576i-50 > /sys/class/graphics/fb0/mode

4. Note

1) For 8 bits BT656 interface, the default data pins are "DISP0_DAT_23~DISP0_DAT_16", it can also

be any other continued display data pins, for example if "DISP0_DAT_7~DISP0_DAT_0" are used, the

macro "BT656_IF_DI_MSB" in "kernel_imx/drivers/mxc/ipu3/ipu_disp.c" should be changed from "23"

to "7".

2) For 16 bits BT1120 interface, the default data pins are "DISP0_DAT_23~DISP0_DAT_8", it can also

be any other continued display data pins, the macro "BT656_IF_DI_MSB" should be modified if the

hardware pins are changed.

3) When bt656 interface is the second display for each IPU,1-layer-fb (it can be checked with command

"$ cat /sys/class/graphics/fbx/fsl_disp_propperty"), the frame buffer can only be YUV format. In this

case, the IPU DC channel was used for BT656 display, it has no CSC function, so RGB frame buffer was

not supported.

2013-08-09 updated:

The new release package "L3.0.35_1.1.0_GA_bt656_output_patch_2013-08-09.zip" had fixed the BT656 dual display issue on iMX6S/DL.

Removed the old release package.

2013-09-04 updated:

The new release package "r13.4.1_bt656_output_patch_2013-09-04.zip" had fixed the BT656 dual display issue on iMX6S/DL.

For default, the dual display was tested with HDMI + CVBS, HDMI is the main display and adv739x CVBS output is the second display.

For iMX6DQ which has two IPUs, please assign dual display to two IPUs, for example adv739x is on IPU1 DI0, it is fixed, because hardware pins used for it is fixed. Then we can assign HDMI or LVDS to another IPU (IPU2).

For iMX6S/DL which has only one IPU, since adv739x had used IPU1 DI0, another display should be IPU1 DI1.

2013-09-30 updated:

Added patch for L3.0.35_4.1.0_GA BSP, the file is "L3.0.35_4.1.0_GA_bt656_output_patch_2013-09-30.zip".

2014-07-21 updated:

Added patch for L3.10.17_1.0.0_GA BSP, the file is "L3.10.17_1.0.0_GA_bt656_output_patch_2014-07-21.zip".

2015-01-26 updated:

Updated the IPU microcode for 1080i50 and 1080i60 BT1120 output, the parameters "N" for command BMA is a 8 bits parameters, so its max value is 255, but for 1080i50 and 1080i60 output, it needs more blank data in each line, the "N" will be bigger than 255, the updated IPU microcode can fix this limitation.

The updated file is "IPU_Microcode_Update_for_BT1120_1080i_20150126.zip". You can update the macro "DC_MCODE_BT656_xxx" and function _ipu_dc_setup_bt656_interlaced() to the old patch if you used BT1120 mode to support 1080i display.

The verified 1080i display mode is:

{

/* 1080I60 Interlaced output */

"BT1120-1080I60", 30, 1920, 1080, 13468,

20, 3,

20, 2,

280, 1,

FB_SYNC_HOR_HIGH_ACT | FB_SYNC_VERT_HIGH_ACT,

FB_VMODE_INTERLACED,

FB_MODE_IS_DETAILED,},

{

/* 1080I50 Interlaced output */

"BT1120-1080I50", 25, 1920, 1080, 13468,

20, 3,

20, 2,

720, 1,

FB_SYNC_HOR_HIGH_ACT | FB_SYNC_VERT_HIGH_ACT,

FB_VMODE_INTERLACED,

FB_MODE_IS_DETAILED,},

2016-01-28 updated:

Updated IPU microcode to align with BT656.4 specification for NTSC output. For other BSP version with NTSC format support, please reference to ipu_disp_update.c for the final microcode.

File "L3.0.35_4.1.0_GA_bt656_output_patch_20160128.zip"., Details, please reference to the readme.txt file in the package.

2016-06-24 update:

Added BT656 and BT1120 progressive mode support.

File "L3.0.35_4.1.0_GA_bt656_output_patch_20160624.zip". Details, please reference to the readme.txt file in the package.

The patch for 3.14.52 GA1.1.0 BSP will be released in next week.

2016-06-27 update:

Add BT656 and BT1120 display patch for 3.14.52 BSP. File "L3.14.52_1.1.0_GA_bt656_output_patch_2016-06-27.zip", details, please reference to the readme.txt in the package.

2017-03-10 update:

Fixed a hard coding DC macro issue for progressive mode. Added patch "0008-Fixed-a-hard-coding-DC-macro-issue-for-progressive-m.patch" in L3.0.35_4.1.0_GA_bt656_output_patch_2017-03-10.zip.

The code in patch "L3.14.52_1.1.0_GA_bt656_output_patch_2016-06-27" is correct.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Qiang,

Thank you very much!

I have one question at last, how to add a config for 720p(1280x720) output?

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

diff --git a/drivers/video/mxc/mxc_bt656if.c b/drivers/video/mxc/mxc_bt656if.c

index 0ad5dee..800ac42 100644

--- a/drivers/video/mxc/mxc_bt656if.c

+++ b/drivers/video/mxc/mxc_bt656if.c

@@ -44,6 +44,7 @@ struct mxc_bt656if_data {

* vsync_len: not used, set to 1

*/

static struct fb_videomode bt656if_modedb[] = {

+ {

+ /* 1280x720 Progressive output */

+ "BT656-720P", 60, 1280, 720, 20833,

+ 25, 5,

+ 0, 0,

+ 732, 1,

+ 0,

+ FB_VMODE_NONINTERLACED,

+ FB_MODE_IS_DETAILED,},

};

static int bt656if_modedb_sz = ARRAY_SIZE(bt656if_modedb);

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks a lot! I will try it.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Qiang,

How to calculate the pclk in 720p mode?

10^12 /((1280*2+25+5+732)*(720+0+0+1)) is not equal 20833

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The 20833 is just a reference setting for pixel clock, you can adjust it.

With the 20833, pixel clock frequency = 10^12 / 20833 = 48MHz, for 60fps setting, the pixel clock should be 148.5MHz, so 20833 should be 6734.

How many pixel clocks for one frame: (1280*2 + 732) * (720 + 25 + 5) = 2469000; so the display refresh rate = 148.5M / 2469000 = 60fps.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear @Qiang Li,

I have a question on xserver settings, for the below mode :

/* NTSC Interlaced output */

+ "BT656-NTSC", 60, 720, 480, 37037,

+ 19, 3,

+ 20, 3,

+ 276, 1,

+ FB_SYNC_HOR_HIGH_ACT | FB_SYNC_VERT_HIGH_ACT,

+ FB_VMODE_INTERLACED,

+ FB_MODE_IS_DETAILED,},

what should be the correct xserver mode settings ? The issue is I cannot get the accelerated frame buffer output to fb0 !!!

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Qiang

Our BSP version is 3.4.52.I want to download the patch "L3.14.52_1.1.0_GA_bt656_output_patch_2016-06-27",but i don't find the driver of adv7393.

Can I download the patch "L3.0.35_4.1.0_GA_bt656_output_patch_2017-03-10",then add this patch in the BSP 3.14.52?

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi llinguo, you can apply the patch "L3.14.52_1.1.0_GA_bt656_output_patch_2016-06-27", then porting the adv739x driver from L3.0.35_4.1.0.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all,

Did anyone try to get PAL out of an ADV7393 chip? NTSC works perfectly, thanks for the effort.

However, PAL seems to be harder on me. I modified the kernel video= boot argument to show PAL. When starting gstreamer test pattern generator, i do get graphics on my PAL monitor. It does, however, seem confused wjth tining somehow. The image seems to flicker, sometimes some grey raster seems to be under the color bars and from the second half, i get the impression that a new frame starts overlapping. The behavior is equally unstable but presents itself somewhat differently on another PAL television I have.

Would this ring a bell for someone?

Thanks a lot

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Sir,

customer ask about hardware connect pads between i.MX6 and ADV7391.

Could use IPU1_DISP0_DAT_23~DISP0_DAT_16 connected to adv7391 P7~P0 pins?

Please help confirm it.

Thanks a lot,

We checked NXP TV box reference design .i.MX6 OTT TVBox HW/SW Reference Design Release (ICS4.0.4_1.0.0-alpha)

P7~P0 pins of ADV7390 is connect i.MX6 IPU_DISP_Data0~7.

We checked the patch in https://community.nxp.com/docs/DOC-94019

Meanwhile find some code about setting DISP_DAT23 ~ DISP_DAT16 or DISP_DAT7 ~ DISP_DAT0 to output “8 bits BT656”

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, it can.

1) For 8 bits BT656 interface, the default data pins are "DISP0_DAT_23~DISP0_DAT_16", it can also

be any other continued display data pins, for example if "DISP0_DAT_7~DISP0_DAT_0" are used, the

macro "BT656_IF_DI_MSB" in "kernel_imx/drivers/mxc/ipu3/ipu_disp.c" should be changed from "23"

to "7".

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

嗨,Hi Qiang

感谢你的工作,我们按照这个文章打了L3.14.52_1.1.0_GA_bt656_output_patch_2016-06-27这个补丁,BT656交错模式下工作正常。

目前我们有新的需求,想通过8位数据线+CLK+VSYNC+HSYNC输出720P的UYVY数据,拟使用引脚如下:

pinctrl_ipu1_bt656: ipu1grp-3 {

fsl,pins = <

MX6QDL_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK 0x10

MX6QDL_PAD_DI0_PIN15__IPU1_DI0_PIN15 0x10

MX6QDL_PAD_DI0_PIN2__IPU1_DI0_PIN02 0x10

MX6QDL_PAD_DI0_PIN3__IPU1_DI0_PIN03 0x10

MX6QDL_PAD_DI0_PIN4__IPU1_DI0_PIN04 0x80000000

MX6QDL_PAD_DISP0_DAT16__IPU1_DISP0_DATA16 0x10

MX6QDL_PAD_DISP0_DAT17__IPU1_DISP0_DATA17 0x10

MX6QDL_PAD_DISP0_DAT18__IPU1_DISP0_DATA18 0x10

MX6QDL_PAD_DISP0_DAT19__IPU1_DISP0_DATA19 0x10

MX6QDL_PAD_DISP0_DAT20__IPU1_DISP0_DATA20 0x10

MX6QDL_PAD_DISP0_DAT21__IPU1_DISP0_DATA21 0x10

MX6QDL_PAD_DISP0_DAT22__IPU1_DISP0_DATA22 0x10

MX6QDL_PAD_DISP0_DAT23__IPU1_DISP0_DATA23 0x10

>;

};

我们的疑问是,在本文补丁下,是否可以支持这么操作,我们该如何配置相关资源?可以给出一些指导意见,谢谢!

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

You can use the BT656 progressive mode to output the 720P display, then use the followed patch to generate VSYNC on DI_PIN3 and HSYNC on DI_PIN2.

In the patch, the VSYNC width is hardcoding as 10 HSYNC (2*10 /* COUNT DOWN */), and the HSYNC width is hardcoding as 80 pixel clocks (2*80 /* COUNT DOWN */), you can modify them as you wanted:

diff --git a/arch/arm/mach-mx6/clock.c b/arch/arm/mach-mx6/clock.c

index 2d5b497..d2d9556 100644

--- a/arch/arm/mach-mx6/clock.c

+++ b/arch/arm/mach-mx6/clock.c

@@ -5556,7 +5556,8 @@ int __init mx6_clocks_init(unsigned long ckil, unsigned long osc,

clk_set_rate(&pll4_audio_main_clk, 176000000);

clk_set_rate(&pll5_video_main_clk, 650000000);

- clk_set_parent(&ipu1_di_clk[0], &pll3_pfd_540M); /* For CVBS 27MHz clock */

+// clk_set_parent(&ipu1_di_clk[0], &pll3_pfd_540M); /* For CVBS 27MHz clock */

+ clk_set_parent(&ipu1_di_clk[0], &pll5_video_main_clk);

clk_set_parent(&ipu1_di_clk[1], &pll5_video_main_clk);

clk_set_parent(&ipu2_di_clk[0], &pll5_video_main_clk);

clk_set_parent(&ipu2_di_clk[1], &pll5_video_main_clk);

diff --git a/drivers/mxc/ipu3/ipu_disp.c b/drivers/mxc/ipu3/ipu_disp.c

index 4dfb194..1d71447 100644

--- a/drivers/mxc/ipu3/ipu_disp.c

+++ b/drivers/mxc/ipu3/ipu_disp.c

@@ -2600,13 +2600,13 @@ int32_t ipu_init_sync_panel(struct ipu_soc *ipu, int disp, uint32_t pixel_clk,

} else if ((pixel_fmt == IPU_PIX_FMT_BT656) || (pixel_fmt == IPU_PIX_FMT_BT1120)) {

pixel_clk = pixel_clk / 10000;

pixel_clk = pixel_clk * 10000;

- if (pixel_clk < 74000000) {

- rounded_pixel_clk = 108000000; /* For PAL and NTSC */

-

- clk_set_rate(di_parent, 540000000);

- clk_set_rate(ipu->di_clk[disp], rounded_pixel_clk);

- clk_set_parent(&ipu->pixel_clk[disp], ipu->di_clk[disp]);

- } else {

+// if (pixel_clk < 74000000) {

+// rounded_pixel_clk = 108000000; /* For PAL and NTSC */

+//

+// clk_set_rate(di_parent, 540000000);

+// clk_set_rate(ipu->di_clk[disp], rounded_pixel_clk);

+// clk_set_parent(&ipu->pixel_clk[disp], ipu->di_clk[disp]);

+// } else {

rounded_pixel_clk = pixel_clk * 2;

rounded_parent_clk = clk_round_rate(di_parent,

rounded_pixel_clk);

@@ -2622,7 +2622,7 @@ int32_t ipu_init_sync_panel(struct ipu_soc *ipu, int disp, uint32_t pixel_clk,

clk_round_rate(ipu->di_clk[disp], pixel_clk);

clk_set_rate(ipu->di_clk[disp], rounded_pixel_clk);

clk_set_parent(&ipu->pixel_clk[disp], ipu->di_clk[disp]);

- }

+// }

} else {

/* try ipu clk first*/

dev_dbg(ipu->dev, "try ipu internal clk\n");

@@ -3123,11 +3123,11 @@ int32_t ipu_init_sync_panel(struct ipu_soc *ipu, int disp, uint32_t pixel_clk,

DI_SYNC_NONE, /* offset resolution */

0, /* repeat count */

DI_SYNC_NONE, /* CNT_CLR_SEL */

- 0, /* CNT_POLARITY_GEN_EN */

+ 1, /* CNT_POLARITY_GEN_EN */

DI_SYNC_NONE, /* CNT_POLARITY_CLR_SEL */

- DI_SYNC_NONE, /* CNT_POLARITY_TRIGGER_SEL */

+ DI_BT656_SYNC_BASECLK, /* CNT_POLARITY_TRIGGER_SEL */

0, /* COUNT UP */

- 0 /* COUNT DOWN */

+ 2*80 /* COUNT DOWN */

);

vsync_cnt = DI_BT656_SYNC_IVSYNC;

@@ -3142,11 +3142,11 @@ int32_t ipu_init_sync_panel(struct ipu_soc *ipu, int disp, uint32_t pixel_clk,

DI_SYNC_NONE, /* offset resolution */

0, /* repeat count */

DI_SYNC_NONE, /* CNT_CLR_SEL */

- 0, /* CNT_POLARITY_GEN_EN */

+ 1, /* CNT_POLARITY_GEN_EN */

DI_SYNC_NONE, /* CNT_POLARITY_CLR_SEL */

- DI_SYNC_NONE, /* CNT_POLARITY_TRIGGER_SEL */

+ DI_BT656_SYNC_HSYNC, /* CNT_POLARITY_TRIGGER_SEL */

0, /* COUNT UP */

- 0 /* COUNT DOWN */

+ 2*10 /* COUNT DOWN */

);

/* COUNTER_5: first active line */

diff --git a/drivers/video/mxc/mxc_bt656if.c b/drivers/video/mxc/mxc_bt656if.c

index 0ad5dee..800ac42 100644

--- a/drivers/video/mxc/mxc_bt656if.c

+++ b/drivers/video/mxc/mxc_bt656if.c

@@ -44,6 +44,7 @@ struct mxc_bt656if_data {

* vsync_len: not used, set to 1

*/

static struct fb_videomode bt656if_modedb[] = {

+#if 0

{

/* NTSC Interlaced output */

"BT656-4-NTSC", 60, 720, 487, 37037,

@@ -161,6 +162,52 @@ static struct fb_videomode bt656if_modedb[] = {

FB_SYNC_HOR_HIGH_ACT | FB_SYNC_VERT_HIGH_ACT,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

+#endif

+ {

+ /* NTSC Progressive output */

+ "BT656-480P", 60, 720, 480, 20833,

+ 36, 9,

+ 0, 0,

+ 276, 1,

+ 0,

+ FB_VMODE_NONINTERLACED,

+ FB_MODE_IS_DETAILED,},

+ {

+ /* PAL Progressive output */

+ "BT656-576P", 50, 720, 576, 20833,

+ 44, 5,

+ 0, 0,

+ 288, 1,

+ 0,

+ FB_VMODE_NONINTERLACED,

+ FB_MODE_IS_DETAILED,},

+ {

+ /* 1280x720 Progressive output */

+ "BT656-720P", 60, 1280, 720, 20833,

+ 25, 5,

+ 0, 0,

+ 732, 1,

+ 0,

+ FB_VMODE_NONINTERLACED,

+ FB_MODE_IS_DETAILED,},

};

static int bt656if_modedb_sz = ARRAY_SIZE(bt656if_modedb);

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

你好,感谢您的及时回复!

按照此回复进行测试,HSYNC和VSYNC可以输出对应信号,HSYNC有效信号等于80个时钟周期,VSYNC有效信号等于10个HSYNC周期,

但是奇怪的是

2*80 /* COUNT DOWN */

以及

2*10 /* COUNT DOWN */

这两个值有约束,比如我们把2*80调整到2*720,或者把2*10调整到2*480,VYSNC以及HSYNC都没有信号了。假设输出480P的UYVY图像

是否2*80应该调整为2*720*2,2*10应该调整为2*(480+消隐行所需行数)?

另外,之前给出的补丁好像是针对L3.0.x版本的,我们用的是L3.14.52版本的内核,没有看到arch/arm/mach-mx6/clock.c b/arch/arm/mach-mx6/clock.c文件,

可否给个L3.14.52版本的补丁,期待你的再次协助,谢谢!

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Display这边输出的HSYNC和VSYNC都是脉冲信号,最大值是255。

如果你们需要输出电平信号的话,就比较复杂了,需要通过对IPU的DI逻辑进行编码,让它输出你们需要的电平信号,这边有一个DI编码的例子,使用DI_PIN04来输出一个DE的信号。https://community.nxp.com/message/392943

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

嗨,还有几个问题想跟你请教下:

1、按照你提供的BT656 720P输出的配置参数

/* 1280x720 Progressive output */

"BT656-720P", 60, 1280, 720, 20833,

25, 5,

0, 0,

732, 1,

0,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

同时我修改了arch/arm/mach-imx/clk-imx6q.c下的时钟

--- a/3-kernel/arch/arm/mach-imx/clk-imx6q.c

+++ b/3-kernel/arch/arm/mach-imx/clk-imx6q.c

@@ -489,8 +489,8 @@ static void __init imx6q_clocks_init(struct device_node *ccm_node)

clk_register_clkdev(clk[IMX6QDL_CLK_ENET_REF], "enet_ref", NULL);

/* ipu clock initialization */

- //imx_clk_set_parent(clk[IMX6QDL_CLK_IPU1_DI0_PRE_SEL], clk[IMX6QDL_CLK_PLL5_VIDEO_DIV]);

- imx_clk_set_parent(clk[IMX6QDL_CLK_IPU1_DI0_PRE_SEL], clk[IMX6QDL_CLK_PLL3_PFD1_540M]);

+ imx_clk_set_parent(clk[IMX6QDL_CLK_IPU1_DI0_PRE_SEL], clk[IMX6QDL_CLK_PLL5_VIDEO_DIV]);

+ //imx_clk_set_parent(clk[IMX6QDL_CLK_IPU1_DI0_PRE_SEL], clk[IMX6QDL_CLK_PLL3_PFD1_540M]);

imx_clk_set_parent(clk[IMX6QDL_CLK_IPU1_DI1_PRE_SEL], clk[IMX6QDL_CLK_PLL5_VIDEO_DIV]);

imx_clk_set_parent(clk[IMX6QDL_CLK_IPU2_DI0_PRE_SEL], clk[IMX6QDL_CLK_PLL5_VIDEO_DIV]);

imx_clk_set_parent(clk[IMX6QDL_CLK_IPU2_DI1_PRE_SEL], clk[IMX6QDL_CLK_PLL5_VIDEO_DIV]);

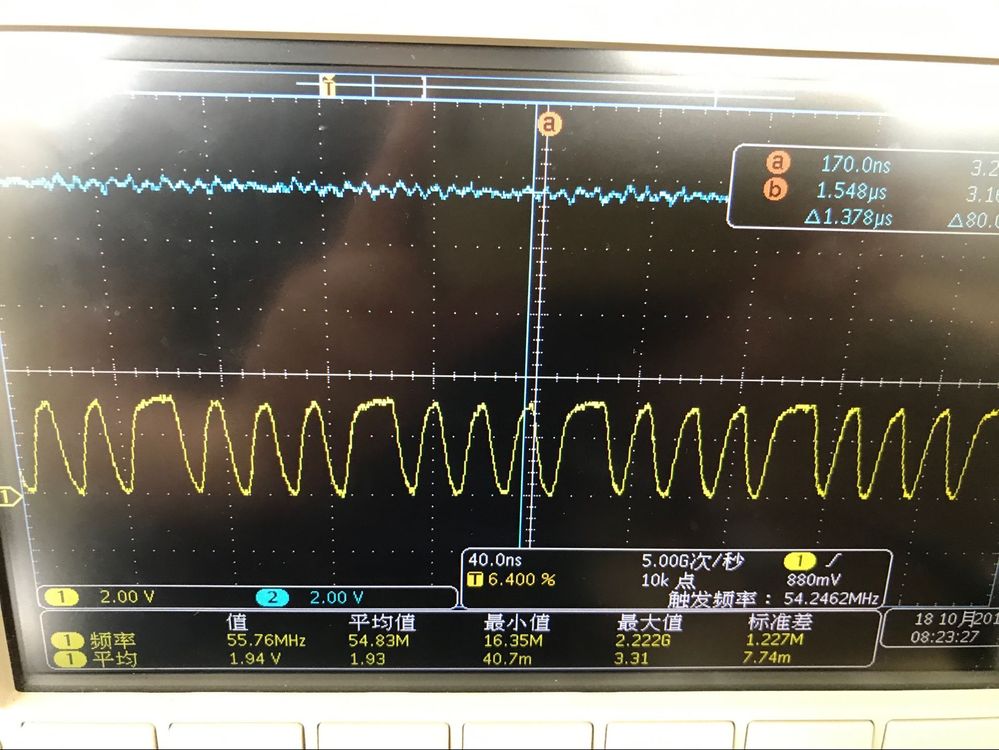

附件是我的ipu_disp.c的补丁文件以及源文件,但是我的时钟波形不正常,如下

请帮忙看下是否哪里我未知的配置不当所致!

--- a/3-kernel/drivers/mxc/ipu3/ipu_disp.c

+++ b/3-kernel/drivers/mxc/ipu3/ipu_disp.c

@@ -3011,7 +3011,7 @@ int32_t ipu_init_sync_panel(struct ipu_soc *ipu, int disp, uint32_t pixel_clk,

0, /* COUNT UP */

0 /* COUNT DOWN */

);

-

+printk(KERN_ALERT "ipu_init_sync_panel, div=%d, h_total=%d, v_total=%d\n", div, h_total, v_total);

/* COUNTER_2: HSYNC for each line */

_ipu_di_sync_config(ipu,

disp, /* display */

@@ -3022,11 +3022,11 @@ int32_t ipu_init_sync_panel(struct ipu_soc *ipu, int disp, uint32_t pixel_clk,

DI_SYNC_NONE, /* offset resolution */

0, /* repeat count */

DI_SYNC_NONE, /* CNT_CLR_SEL */

- 0, /* CNT_POLARITY_GEN_EN */

+ 1, /* CNT_POLARITY_GEN_EN */

DI_SYNC_NONE, /* CNT_POLARITY_CLR_SEL */

- DI_SYNC_NONE, /* CNT_POLARITY_TRIGGER_SEL */

+ DI_BT656_SYNC_BASECLK, /* CNT_POLARITY_TRIGGER_SEL */

0, /* COUNT UP */

- 2*div /* COUNT DOWN */

+ 2*80 /* COUNT DOWN */

);

vsync_cnt = DI_BT656_SYNC_IVSYNC;

@@ -3041,11 +3041,11 @@ int32_t ipu_init_sync_panel(struct ipu_soc *ipu, int disp, uint32_t pixel_clk,

DI_SYNC_NONE, /* offset resolution */

0, /* repeat count */

DI_SYNC_NONE, /* CNT_CLR_SEL */

- 0, /* CNT_POLARITY_GEN_EN */

+ 1, /* CNT_POLARITY_GEN_EN */

DI_SYNC_NONE, /* CNT_POLARITY_CLR_SEL */

- DI_SYNC_NONE, /* CNT_POLARITY_TRIGGER_SEL */

+ DI_BT656_SYNC_HSYNC, /* CNT_POLARITY_TRIGGER_SEL */

0, /* COUNT UP */

- 0 /* COUNT DOWN */

+ 2*10 /* COUNT DOWN */

);

/* COUNTER_5: first active line */

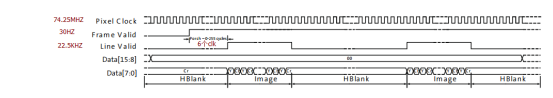

2、在此之前我们完成了720P摄像头通过BT656接口外同步的接入,其时序如下:

分辨率:1280*720

输出数据格式:YUV 8bit

帧率:30fps

PIXCLK=74.25MHZ

VS=30HZ

HS=22.5KHZ

目前我们想做的希望能通过BT656的外同步输出产生类似这种的波形,不知是否可以实现?

3、根据第2点的时序要求我把补丁上的时钟参数20833调整到13468,测量了PIXCLK、VSYNC、HSYNC是符合第2点所示频率的。在这种外同步非交错模式下,下面这些参数是如何的出来的,是否有对应的计算方法,可否提供些这方面的资讯

20833,

25, 5,

0, 0,

732, 1,

4、按照目前你给出的补丁配置,显示缓冲中的UYVY数据是什么时机通过8位数据总线输出的,就是说数据输出跟同步信号是如何配合的,是在HSYNC的上升沿输出UYVY数据还是下降沿,是HSYNC的上升沿停止输出还是下降沿停止输出?在目前的这个配置下,应该不再有SAV/EAV以及消隐数据的输出了吧?问题有点初级,见谅!

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

1. ipu_disk.c里面漏改以下代码,108M的clock适用于标准的BT656输出,不适用你现在的设置:

- if (pixel_clk < 74000000) {

- rounded_pixel_clk = 108000000; /* For PAL and NTSC */

-

- clk_set_rate(di_parent, 540000000);

- clk_set_rate(ipu->di_clk[disp], rounded_pixel_clk);

- clk_set_parent(&ipu->pixel_clk[disp], ipu->di_clk[disp]);

- } else {

+// if (pixel_clk < 74000000) {

+// rounded_pixel_clk = 108000000; /* For PAL and NTSC */

+//

+// clk_set_rate(di_parent, 540000000);

+// clk_set_rate(ipu->di_clk[disp], rounded_pixel_clk);

+// clk_set_parent(&ipu->pixel_clk[disp], ipu->di_clk[disp]);

+// } else {

2. 之前提过了,HSYNC和VSYNC作为display输出,默认是出脉冲信号的,不是camera这样的电平信号;但是如果blank比较少的话(比如小于255),是可以让它输出你需要的电平信号的。

3. 下面的参数是一个测试的输出,pixel clock = 1000000 / 20833 = 48MHz; 有效数据是1280*720,VSYNC的blank行是 25+5 = 30行,HSYNC的blank 就是732个Pixel clock,最后的1不使用。帧率 = 48000000 / ((30 + 720) * (732 + 1280*2)) = 19.44 fps

20833,

25, 5,

0, 0,

732, 1,

4. 数据线上EAV/SAV还是有的,只是同时有HSYNC和VSYNC输出,patch里面的设置:

0, /* COUNT UP */

2*80 /* COUNT DOWN */

上面这个是HSYNC的,按3的参数,HSYNC总的blank是732个pixel clock,HSYNC在第一个clock时拉高,保持80个clock,然后变低;HSYNC的极性可以在ipu_disp.c,函数ipu_init_sync_panel的以下代码进行反转:

if (sig.Hsync_pol) {

di_gen |= DI_GEN_POLARITY_2;

0, /* COUNT UP */

2*10 /* COUNT DOWN */

上面这个是VSYNC的,按3的参数,VSYNC总的blank是30行,VSYNC在第一行时拉高,保持10行,然后变低;VSYNC的极性可以在ipu_disp.c,函数ipu_init_sync_panel的以下代码进行反转:

if (sig.Vsync_pol) {

di_gen |= DI_GEN_POLARITY_3;

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

非常感谢您的详尽回复,让我们对很多疑点清晰明朗了。

总之,就是在BT656模式下,数据流仍然是BT656标准格式的,只是同时可以输出HSYNC以及VSYNC同步信号。

但是在其它帖子中,我看您有提到VSYNC/HSYNC模式,并且有下面解释:

For VSYNC/HSYNC mode, it means there no EAV/SAV data on data line, only video data are sent on data line, all timing signals are sent on VSYNC and HSYNC pins.

那么我还想了解下,BT656数据线接口下(8位数据总线),目前的程序是否支持VSYNC/HSYNC模式进行显示输出,如果不支持是否可以补丁支持,这个工作量大否?因为我们做成的还是没有EAV/SAV输出的纯UYVY数据流模式.

另外,你有提到DE信号的输出,可否再进一步的结合现有的程序解释下,现在的代码中是否有DE输出的控制,使用的是那个引脚,您上面回复提示的使用不同的引脚输出DE信号的好像是基于3.0.xx版本的,可否给出个3.14.52版本的实例?

最后DE信号是否只有在LCD接口下才能用?

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

"BT656数据线接口下(8位数据总线),目前的程序是否支持VSYNC/HSYNC模式进行显示输出" 这个在之前的回复里面,应该已经给出建议如何实现了,EAV/SAV都是在blank时间输出的,对按照HSYNC/VSYNC接收没什么影响,你可以实际测量波形看看,只要blank不超过255,应该都是可以的。这个在目前情况下,是最容易做的。

非BT656的8位UYVY+HSYNC/VSYNC输出,IPU也是可以支持的,主要要修改IPU这边的设置,让它用2个pixel clock输出一个像素,不过没有现成的patch,你们需要自行开发,这个需要对IPU的DI部分非常了解才行。

IPU的代码和kernel版本基本无关的,DE这个例子,只是告诉你,通过对IPU DI的编码,可以让IPU_DI_PIN输出任何你需要的波形。

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

嗨,Qiang

感谢耐心回复,现在我们明白如何实施了,再次感谢!

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Qiang-Li,

I use ADV7342 chip as a TV encoder which can also accept 16 bit pixel bus (16-bit YCbCr input). Anyway it does not support EAV/SAV, so I plan to use external VSYNC and HSYNC for that. Can I use BT1120 mode for this ? If yes what would be the pixel format for the frame buffer ?

fb_lcd{

if_fmt = BT1120;

if_pixel_fmt = ?

}

Moreover can we use an RGB pixel format for BT656 8-bit mode ?

Thanks in Advance

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Anuradha,

For 16-bit YCbCr with HSYNC and HSYNC, you can reference to this patch:

https://community.nxp.com/docs/DOC-100657

video=mxcfb0:dev=lcd,LCD-1080i50,if=UYVY16,fbpix=RGB32

"if=UYVY16" means 16-bit YCbCr with HSYNC and HSYNC output mode. You can add your own timing mode to replace the "LCD-1080i50" mode, the default BSP can't support UYVY16 mode output, it is enabled in that patch.

For "RGB pixel format for BT656 8-bit mode", it can be supported too, you can use the DC for display, then no CSC, and the RGB data in framebuffer can be sent to 8 bit LCD interface directly.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi thanks for your reply. Can fbpix be RGB in UYVY16 interface mode ? I noticed in mxc_ipuv3_fb.c, always the fb pixel format is YUYV or UYVY for UYVY16 interface !!

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Display interface and framebuffer format can be different, just like the BT656 output, on display interface, it is 8 bits UYVY data, but in framebuffer, it can be RGB565, RGB32 ... ...

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Qiang,

So in this TV encoder, 16-bit mode requires 2 clock cycles per pixel. Is it available under BT1120 mode in ipu_disp.c ? How to set the number of clock cycles required for pixel in ipu files ?

Thanks

Anuradha

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Just simply doing this, can we get 2 clocks per pixel :

/* Active Pixel */

_ipu_di_sync_config(ipu,

disp, /* display */

DI_SYNC_APIXEL, /* counter */

0, /* run count */

DI_SYNC_CLK * 2, /* run_resolution */

h_start_width + h_sync_width, /* offset */

DI_SYNC_CLK, /* offset resolution */

width, /* repeat count */

DI_SYNC_ALINE, /* CNT_CLR_SEL */

0, /* CNT_POLARITY_GEN_EN */

DI_SYNC_NONE, /* CNT_POLARITY_CLR_SEL */

DI_SYNC_NONE, /* CNT_POLARITY_TRIGGER_SEL */

0, /* COUNT UP */

0 /* COUNT DOWN */

);

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, what is your idea about dual clock mode. Can I achieve this using DI_SYNC_CLK * 2, /* run_resolution */ ?

Thanks

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

For BT656 mode, it is already two pixel clock to send out one pixel data. And this patch will not work with your "DI_SYNC_CLK * 2, /* run_resolution */" modification.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Mm.... strange, if you check the link you gave me,

Patch for iMX6 BSP to support interlaced display on HDMI and LCD interface

in 4th comment you've mentioned DI_SYNC_CLK * 2, /* run_resolution */ should work. That's why I asked about it.

Anuradha

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

For that interlaced display patch, you can use such kind of double clock mode.

I had tested on parallel LCD, for a 800*480 display, I can set the framebuffer to 400*480, and use that kind of double clock mode, the display can work fine.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Qiang

We're using Linux 4.1.15 on IMX6Q platform, and do you have patch for Linux 4.1.15?

Or some patch here for Linux 3.x can also be used for Linux 4.1.15?

Thanks for your help.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We also use 4.1.15 and need the patch for this version.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Any news on the availability of the patch for L4.1.15?

If I have to port it on my own, what would be the best starting point? L3.14.52_1.1.0_GA_bt656_output_patch_2016-06-27.zip?

Best regards

Martin

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello everyone.

I would like to try this patch.

Where can I obtain the original source file to which patches can be applied?

I tried two source files, but I get an error.

https://github.com/embeddedarm/linux-3.0.35-imx6-android

https://github.com/ADVANTECH-Corp/linux-imx6

Thank you for your support.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello All,

I too need this patch for L4.1.15.

Has anybody got this?

Ian

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Qiang ,

Where can I get the patch for the IPU output the parallel video format YUV422 8bit with Hsync Vsync DE Pclk signals ?

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

yes, I think so, if you need to use mxcfb1, thy to set in the uboot command. for restriction, ipu can support up to 240M. for pixel clock set, you can refer to the patch and source code in the bsp cleanmaster.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

你好,我们板卡采用是imx6q汽车级芯片,用来做安防监控,自己的板卡硬件参考英贝特sabrelite开发板修改。

内核版本采用linux-3.0.35版本,板卡上CVBS输出和HDMI输出两种接口。CVBS输出采用adv7391芯片。ADV7391芯片温度范围-40℃~85℃。

驱动我下载您发布的 L3.0.35_4.1.0_GA_bt656_output_patch_2017-03-10.zip 版本,按照补丁中方法,以此打补丁,并且成功。补丁打完之后修改了board-mx6q_sabrelite.c文件,增加了对adv7391 IIC设备的支持。 也对管脚进行初始化,管脚初始化如下代码:

/* DISPLAY RGB新增代码*/

/*New Code for Board

原开发板sabrelite接口使用MX6_PAD_DISP0_DAT0~MX6_PAD_DISP0_DAT23 24位

新板子 DIS0外接ADV7391BCPZ 使用8位总线*/

MX6Q_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK, /*DISP0_CLK*/

//MX6Q_PAD_DI0_PIN15__IPU1_DI0_PIN15, /* DE */

MX6Q_PAD_DI0_PIN2__IPU1_DI0_PIN2, /* DISP0_HSYNC */

MX6Q_PAD_DI0_PIN3__IPU1_DI0_PIN3, /* DISP0_VSYNC */

MX6Q_PAD_DI0_PIN4__IPU1_DI0_PIN4,

MX6Q_PAD_DI0_PIN4__GPIO_4_20, /* CVBS_nRST */

MX6Q_PAD_DISP0_DAT0__IPU1_DISP0_DAT_0,

MX6Q_PAD_DISP0_DAT1__IPU1_DISP0_DAT_1,

MX6Q_PAD_DISP0_DAT2__IPU1_DISP0_DAT_2,

MX6Q_PAD_DISP0_DAT3__IPU1_DISP0_DAT_3,

MX6Q_PAD_DISP0_DAT4__IPU1_DISP0_DAT_4,

MX6Q_PAD_DISP0_DAT5__IPU1_DISP0_DAT_5,

MX6Q_PAD_DISP0_DAT6__IPU1_DISP0_DAT_6,

MX6Q_PAD_DISP0_DAT7__IPU1_DISP0_DAT_7,

修改文件 linux3.0.35/drivers/mxc/ipu3/ipu_disp.c 62行

将宏定义23修改成7

#define BT656_IF_DI_MSB 7// 23

/* For 8 bits BT656: 23 for DISP_DAT23 ~ DISP_DAT16; 7 for DISP_DAT7 ~ DISP_DAT0 */

/* For 16 bits BT1120: 23 for DISP_DAT23 ~ DISP_DAT8; 15 for DISP_DAT15 ~ DISP_DAT0 */

下面是我个人打补丁的记录:

linux@ubuntu:~/workspace/mx6q/linux-3.0.35$ patch -p1 < 0001-Support-BT656-and-BT1120-output-for-iMX6-ipuv3.patch

patching file arch/arm/configs/imx6_defconfig

patching file arch/arm/mach-mx6/board-mx6q_sabresd.c

patching file arch/arm/mach-mx6/devices-imx6q.h

patching file arch/arm/plat-mxc/include/mach/ipu-v3.h

patching file drivers/media/video/mxc/output/mxc_vout.c

patching file drivers/mxc/ipu3/ipu_common.c

patching file drivers/mxc/ipu3/ipu_device.c

patching file drivers/mxc/ipu3/ipu_disp.c

patching file drivers/mxc/ipu3/ipu_regs.h

patching file drivers/video/mxc/Kconfig

patching file drivers/video/mxc/Makefile

patching file drivers/video/mxc/mxc_bt656if.c

patching file drivers/video/mxc/mxc_ipuv3_fb.c

patching file include/linux/ipu.h

patching file include/linux/mxcfb.h

linux@ubuntu:~/workspace/mx6q/linux-3.0.35$ patch -p1 < 0002-Support-adv739x-TV-encoder-for-BT656-output.patch

patching file arch/arm/mach-mx6/board-mx6q_sabresd.c

patching file drivers/video/mxc/Kconfig

patching file drivers/video/mxc/Makefile

patching file drivers/video/mxc/mxcfb_adv739x.c

linux@ubuntu:~/workspace/mx6q/linux-3.0.35$ patch -p1 < 0003-Enhance-dual-display-support-for-BT656-output.patch

patching file arch/arm/mach-mx6/board-mx6q_sabresd.c

patching file arch/arm/mach-mx6/clock.c

patching file arch/arm/plat-mxc/include/mach/ipu-v3.h

patching file drivers/media/video/mxc/capture/ipu_bg_overlay_sdc.c

patching file drivers/media/video/mxc/capture/ipu_csi_enc.c

patching file drivers/media/video/mxc/capture/ipu_fg_overlay_sdc.c

patching file drivers/media/video/mxc/capture/ipu_prp_enc.c

patching file drivers/media/video/mxc/capture/ipu_prp_vf_sdc.c

patching file drivers/media/video/mxc/capture/ipu_prp_vf_sdc_bg.c

patching file drivers/media/video/mxc/capture/ipu_still.c

patching file drivers/mxc/ipu3/ipu_common.c

patching file drivers/mxc/ipu3/ipu_device.c

patching file drivers/mxc/ipu3/ipu_disp.c

patching file drivers/mxc/ipu3/ipu_prv.h

patching file drivers/video/mxc/mxc_ipuv3_fb.c

linux@ubuntu:~/workspace/mx6q/linux-3.0.35$ patch -p1 < 0004-BT656-Display-updated-for-BT1120-1080i-support.patch

patching file drivers/mxc/ipu3/ipu_disp.c

patching file drivers/video/mxc/mxc_bt656if.c

linux@ubuntu:~/workspace/mx6q/linux-3.0.35$ patch -p1 < 0005-Update-IPU-microcode-to-align-with-BT656.4-specifica.patch

patching file drivers/mxc/ipu3/ipu_disp.c

patching file drivers/video/mxc/mxc_bt656if.c

patching file drivers/video/mxc/mxcfb_adv739x.c

linux@ubuntu:~/workspace/mx6q/linux-3.0.35$ patch -p1 < 0006-Set-Y-range-16-235-U-V-range-16-240-for-BT656-displa.patch

patching file drivers/mxc/ipu3/ipu_disp.c

linux@ubuntu:~/workspace/mx6q/linux-3.0.35$ patch -p1 < 0007-Add-progressive-mode-support-for-BT656-and-BT1120-di.patch

patching file drivers/mxc/ipu3/ipu_disp.c

patching file drivers/video/mxc/mxc_bt656if.c

patching file drivers/video/mxc/mxc_ipuv3_fb.c

linux@ubuntu:~/workspace/mx6q/linux-3.0.35$ patch -p1 < 0008-Fixed-a-hard-coding-DC-macro-issue-for-progressive-m.patch

patching file drivers/mxc/ipu3/ipu_disp.c

linux@ubuntu:~/workspace/okmx6q/linux-3.0.35$

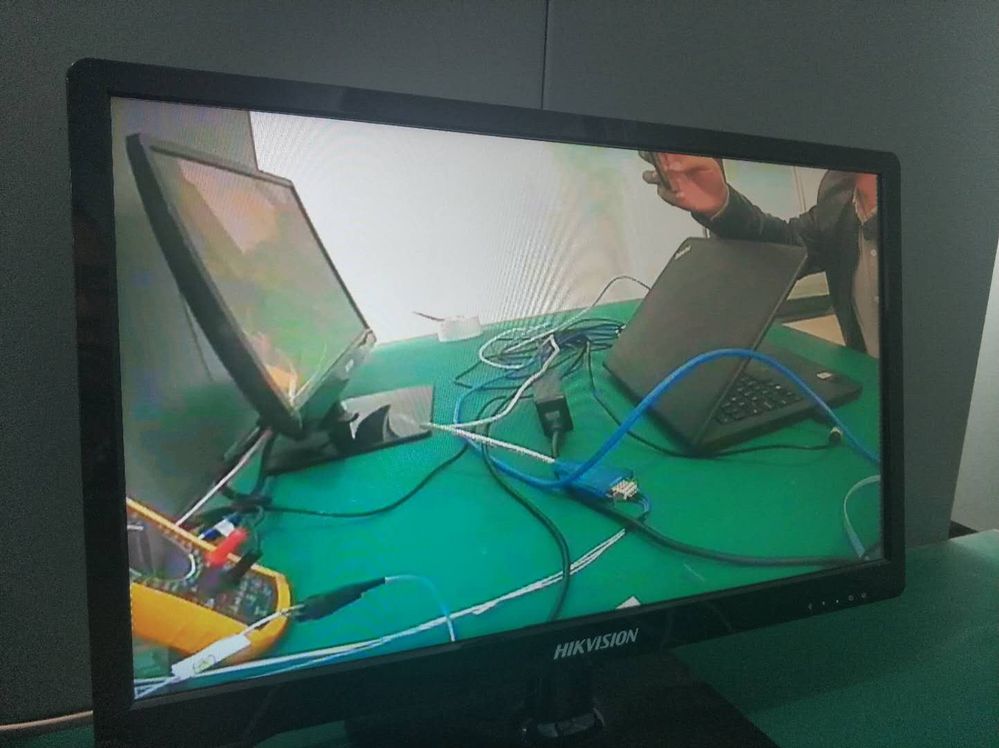

所有补丁完成之后,并且修改完成, 板卡在常温下可以正常显示视频图像,并且稳定,显示如下图:

板卡做低温试验 条件-40℃ 图像显示如下,adv7391驱动集成到内核当中,可能性的会造成内核启动时候跑飞。如果去掉adv7391驱动,内核不会跑飞,环境变量修改参数换成HDMI显示则正常工作。

以下是一些参数配置

# cat /sys/class/graphics/fb0/fsl_disp_dev_property

arch\arm\mach-mx6\clock.c 配置成了

clk_set_parent(&ipu1_di_clk[0], &pll3_pfd_540M); //for CVBS 27MHz clock

clk_set_parent(&ipu1_di_clk[1], &pll5_video_main_clk);

环境变量配置成了

"video=mxcfb0:dev=adv739x,BT656-PAL,if=BT656,fbpix=RGB565"

以上是我的参数.

望指教!

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi yan zhang

The I2C interface is the only interface iMX6 will read from adv7391, so I think you need check the I2C signal in -40 degree case, maybe the drive stregth for the I2C pins need be increased.

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

您好。我们这边使用L3.14.28版本的内核,CPU使用i.mx6q,手动打上以上L3.14.52_1.1.0_GA_bt656_output_patch_2016-06-27之后,如果arch/arm/mach-imx/clk-imx6q.c中的clock配置保持原来的

imx_clk_set_parent(clk[IMX6QDL_CLK_IPU1_DI0_PRE_SEL],clk[IMX6QDL_CLK_PLL5_VIDEO_DIV]);

则可以正常输出BT1120数据,格式是1280*720@25,时钟频率为74.25MHz,但此时与HDMI无法双显;

如果把以上配置改为patch中的

mx_clk_set_parent(clk[IMX6QDL_CLK_IPU1_DI0_PRE_SEL], clk[IMX6QDL_CLK_PLL3_PFD1_540M]);

则BT1120无法输出。

无奈我们现在的应用必须使用双显,请问,将IPU1_DI0的时钟源选择为PLL3_PFD1_540M,还需要另外什么配置,才可以使BT1120正确输出吗?或者如果这个时钟源做不到这个频率,是否还有别的办法?盼回复,多谢。

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

If you need HDMI to support different resolutions, then it has to use PLL5 alone. If your HDMI just need support some special resolution, then you can set PLL5 to a fixed frequency, and let BT1120 and HDMI to generate pixel clock from it. For example, if PLL5 is 594MHz, it can support 1080P HDMI (148.5MHz pixel clock) + BT1120 (74.25MHz pixel clock) together.

Except the programable PLL5, the IPU_DI clock source can be followed:

mmdc_ch0_axi 528MHz

pll3_usb_otg 480MHz

pll2_pfd0_352m

pll2_pfd2_396m

pll3_pfd1_540m

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Somebody already ported the patch to kernel 4.9.123?

I tried to port this but got stuck. At boot I got a kernel panic saying "Failed set parent clk"

After comparing the source I found out there are some things changed to the clk initialization in the new kernel, compared to 4.1.15.

Clint

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Qiang_FSL谢谢您的回复。我这边现在HDMI需要使用720 * 576的分辨率,按您的描述,看来是无法使用PLL5同时作为BT1120和HDMI的时钟了。我现在可以使用以下时钟的哪一个来作为IPU1_DI0 (BT1120 1280*720@25)的输出使用吗?如果可以,clk-imx6q.c中应该怎么改呢?

mmdc_ch0_axi 528MHz

pll3_usb_otg 480MHz

pll2_pfd0_352m

pll2_pfd2_396m

pll3_pfd1_540m

我有尝试过将IPU1_DI0的时钟源配置为pll3_pfd1_540m:mx_clk_set_parent(clk[IMX6QDL_CLK_IPU1_DI0_PRE_SEL], clk[IMX6QDL_CLK_PLL3_PFD1_540M]);,然后通过struct fb_videomode中的pixclock来修改输出时钟,发现会有BT1120画面输出,但颜色失真严重,时钟无法完美做到74.25MHz。谢谢。

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

你可以把pll3_pfd1_540m给HDMI的720 * 576显示,把PLL5给BT1120的1280*720@25。

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Qiang Li - Mpu Se 撰写:

你可以把pll3_pfd1_540m给HDMI的720 * 576显示,把PLL5给BT1120的1280*720@25。

谢谢。我之前有尝试过把pll3_pfd1_540m给HDMI使用,我的HDMI配置的是IPU1_DI1,所以clk-imx6q.c中做了如下修改:mx_clk_set_parent(clk[IMX6QDL_CLK_IPU1_DI1_PRE_SEL], clk[IMX6QDL_CLK_PLL3_PFD1_540M]);,HDMI就无输出,改回PLL5就会有画面输出。我不确定是否还有其它地方需要修改?

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

zheng fudi ,你需要跟一下clock,看看频率设置的对不对。

- 既読としてマーク

- 新着としてマーク

- ブックマーク

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Qiang Li 您好!

我现在用的imx6d+L3.14.52,通过BT656输出pixelclock=74.25MHz,1280x720@30时可以正常输出,如果输出1280x720@25系统提示有问题,不能正常工作,系统提示:_ipu_dc_setup_bt656_progressive: bt656 interface is not supported in mode 4.

查找原因应该是BT656输出horizontal blanking的值不能大于0x200导致,1280x720@25的参数如下:

{

/* 720P25 Progressive output */

"BT656-720P25", 25, 1280, 720, 13468, //13889,

20, 10,

0, 0,

1400, 1,

FB_SYNC_HOR_HIGH_ACT | FB_SYNC_VERT_HIGH_ACT,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

主要原因应该是是上面1400的这个值超出了范围,因为后芯片PT1000K是bt656转AHD 1280X720@25p输出,对应的BT656输出的像素时钟只能为74.25MHz,无法降低像素时钟频率来减少horizontal blanking的值,麻烦您帮忙看一下这个问该如何解决?是不要更改microcode的,要如何更改?谢谢了

错误输出应该是文件ipu_disp.c中下面的代码产生的:

// loop_blank_video_times max value is 255, 8 bits

if(is_bt1120)

temp = bt656_h_start_width - 8; //horizontal blanking + 1

else

temp = (bt656_h_start_width - 8) / 2; //horizontal blanking + 1

if (temp < 0x100) {

loop_N_mode = 1;

loop_blank_video_times = temp - 1;

} else if (temp < 0x200) {

if ((temp & 0x1) != 0) {

dev_err(ipu->dev, "_ipu_dc_setup_bt656_progressive: bt656_h_start_width is not aligned in mode 2.\n");

return;

}

loop_N_mode = 2;

loop_blank_video_times = (temp / 2) - 1;

} else if (temp < 0x400) {

if ((temp & 0x3) != 0) {

dev_err(ipu->dev, "_ipu_dc_setup_bt656_progressive: bt656_h_start_width is not aligned in mode 4.\n");

return;

}

if (!is_bt1120) {

dev_err(ipu->dev, "_ipu_dc_setup_bt656_progressive: bt656 interface is not supported in mode 4.\n");

return;

}

loop_N_mode = 4;

loop_blank_video_times = (temp / 4) - 1;

} else {

dev_err(ipu->dev, "_ipu_dc_setup_bt656_progressive: bt656_h_start_width = %d is too big.\n", bt656_h_start_width);

return;

}

loop_frame_blank_line_times = bt656_v_start_width + bt656_v_end_width - 1; //Vertical Blanking lines for one frame