- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- Tシリーズ

- :

- T2081 CPU frequency configuration

T2081 CPU frequency configuration

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

T2081 CPU frequency configuration

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We are facing an issue of wrong configuration of T2081 Processor and this issue is intermittent.

Whenever our custom board is powered ON the Processor configures itself with the RCW in the NOR flash. We have configured 1200MHz CPU frequency in the RCW. UART interface is programmed for 115200 baud rate. When the UART interface comes up with 115200 baud rate we are able to see the CPU is configured for 1200MHz of CPU frequency.

Sometimes at power ON the UART is not able to configure at 115200 baud rate and the screen shows junk information. At this point if the RS232 at the PC end is configured for 57600 baud rate I am able to see the display with CPU frequency configured for 2400MHz.

And this change in CPU frequency occurs only at power ON. Once the Processor is configured for a particular frequency and I assert the Poreset pin the same frequency is maintained constantly.

Can someone help me in knowing why and where the configuration is changing on the board?

I am sending the Linux logs for the CPU configured for 1200MHz and 2400MHz frequency as attachment.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Out of 5 boards 2 boards are having the issue of frequency being different than what is configured. Can you please let me know the address of PORPLLSR register?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There is no PORPLLSR in the T2080.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Fedor,

We have tested flash IC by writing, reading, blank checking and verifying the data. We are able to write and read properly multiple times. Which means the flash IC is working fine.

Read the register CLKCG1HWACSR and we have read HWACLKSEL bits as "0110 CGA PLL2 divide-by-2" instead of "0001 CGA PLL1 divide-by-1" as configured in RCW.

I would like to know why the register is reading wrong values than the values which are programmed in Flash RCW.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

> we have read HWACLKSEL bits as "0110 CGA PLL2 divide-by-2"

This could indicate a power-on issue.

Refer to the QorIQ T2081 Data Sheet and check:

- power sequencing

- power supply ramp rate

- supply voltages

- reset initialization signals timings

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Fedor,

On our board the core supply is up after around 30ms after our FPGA boots up. Can I add 100ms to 500ms additional delay for the core power to come up after the FPGA boots up along with the IO voltages like 1.8V and 2.5V.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please provide complete power-on diagram.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Fedor,

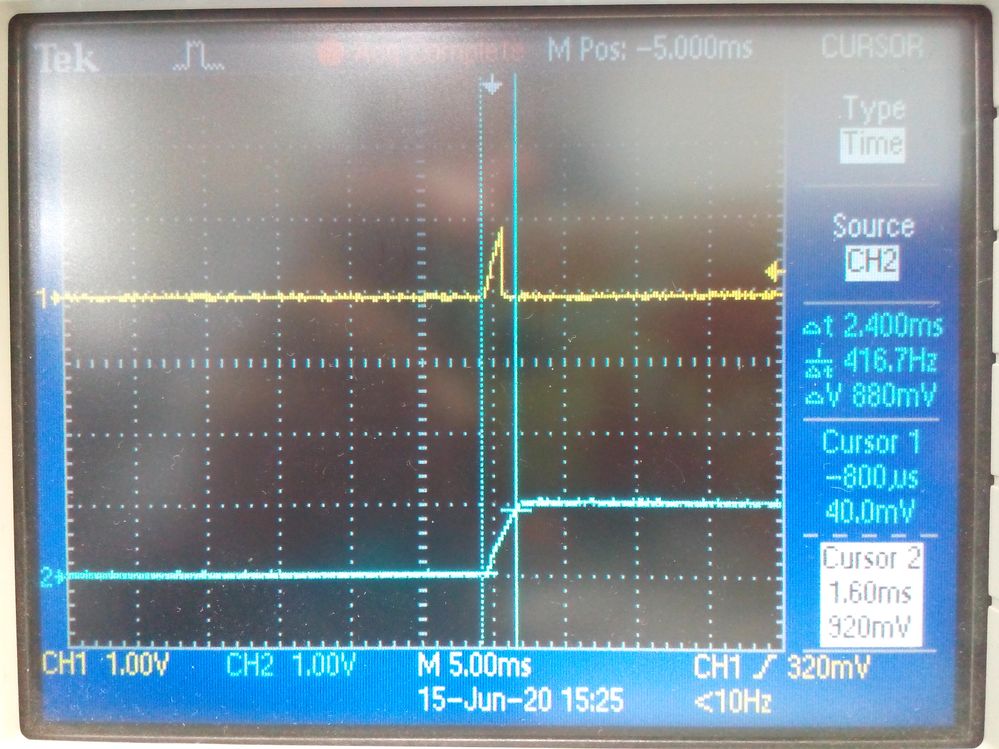

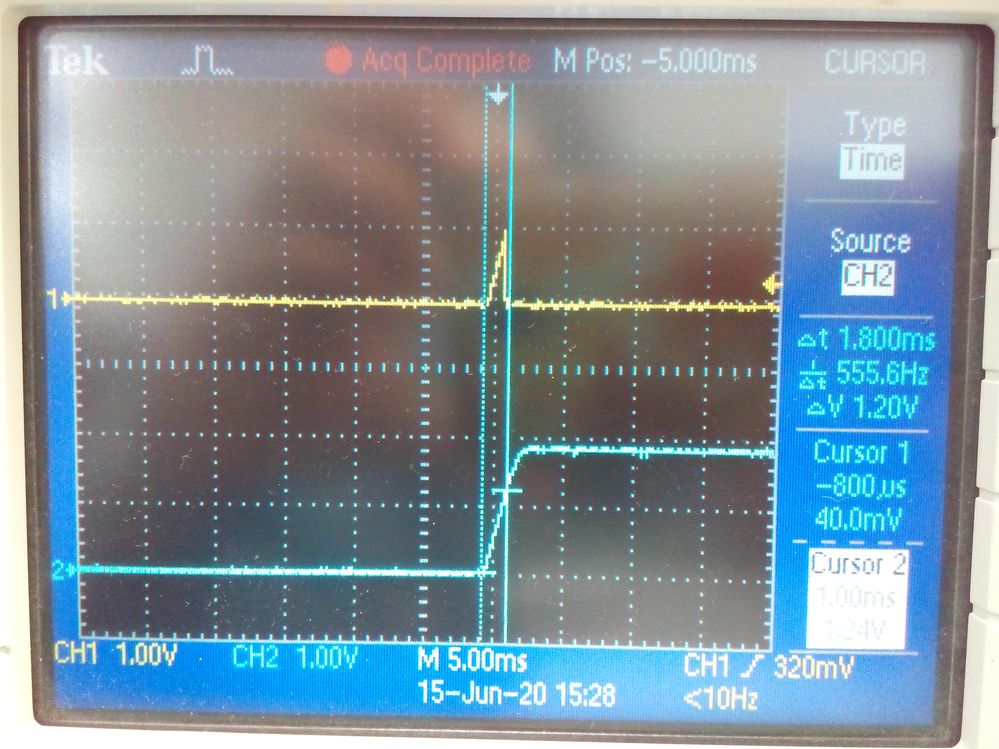

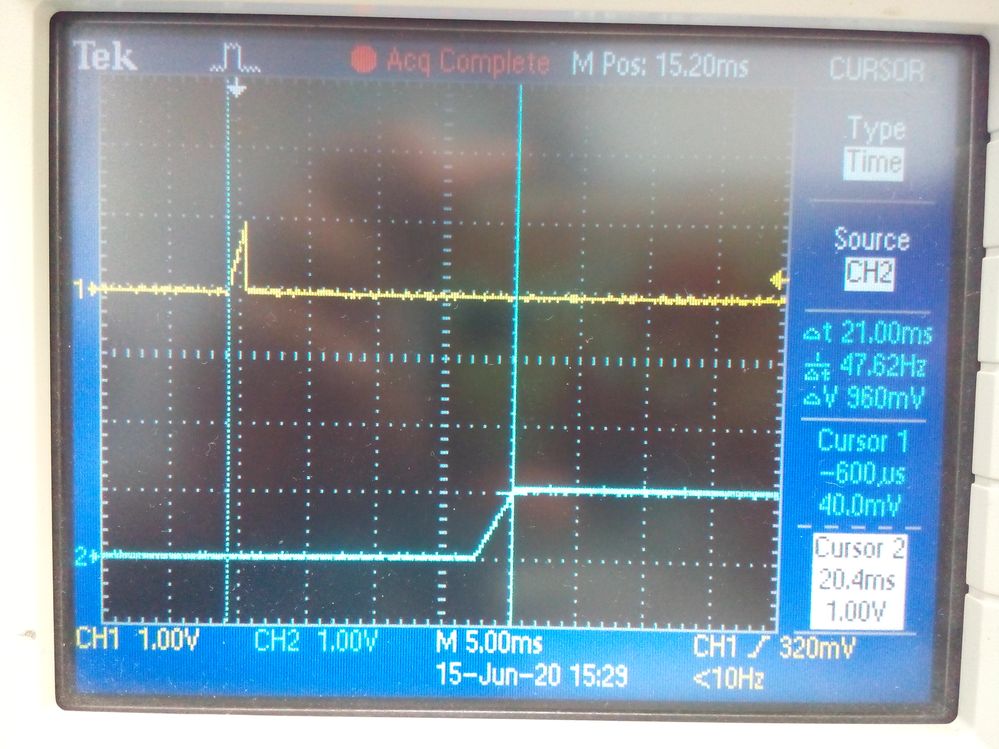

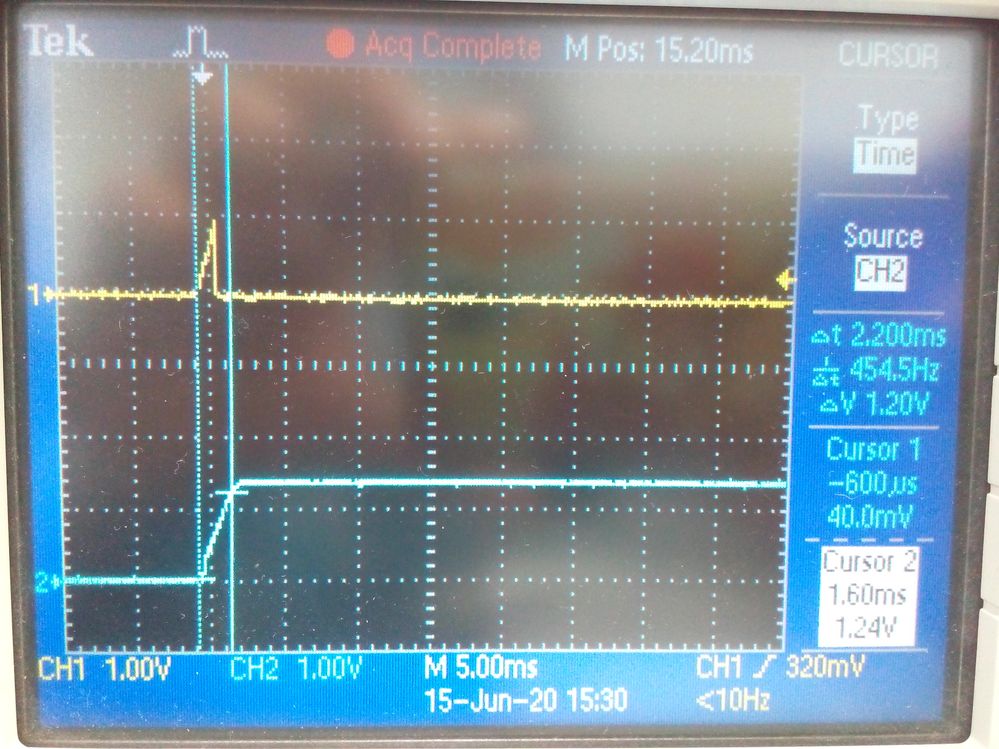

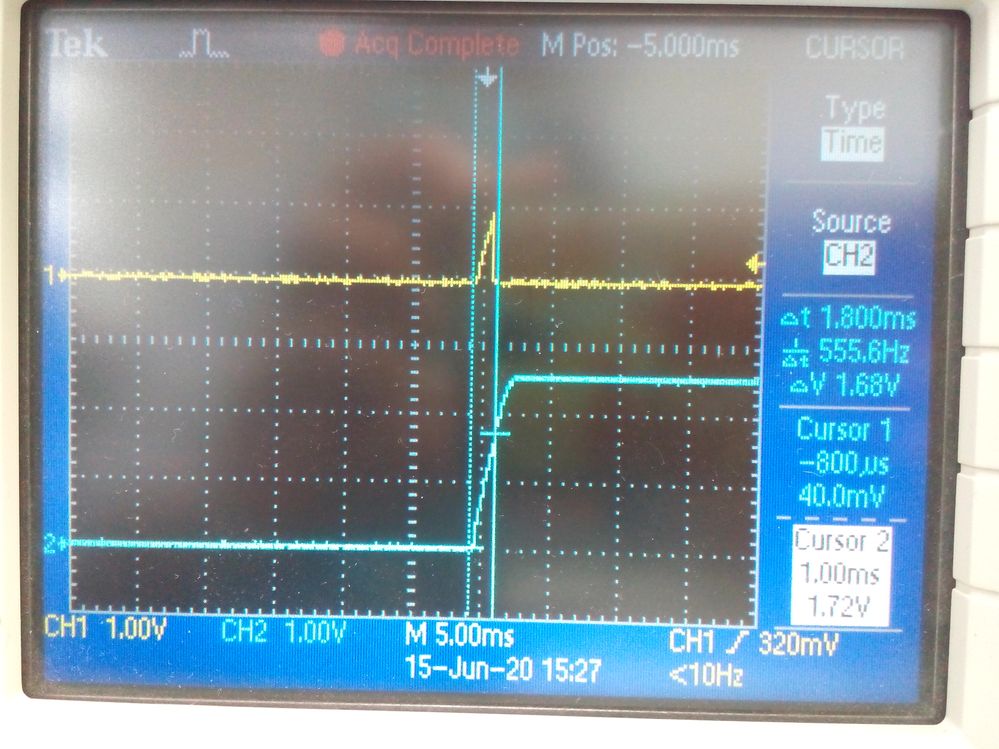

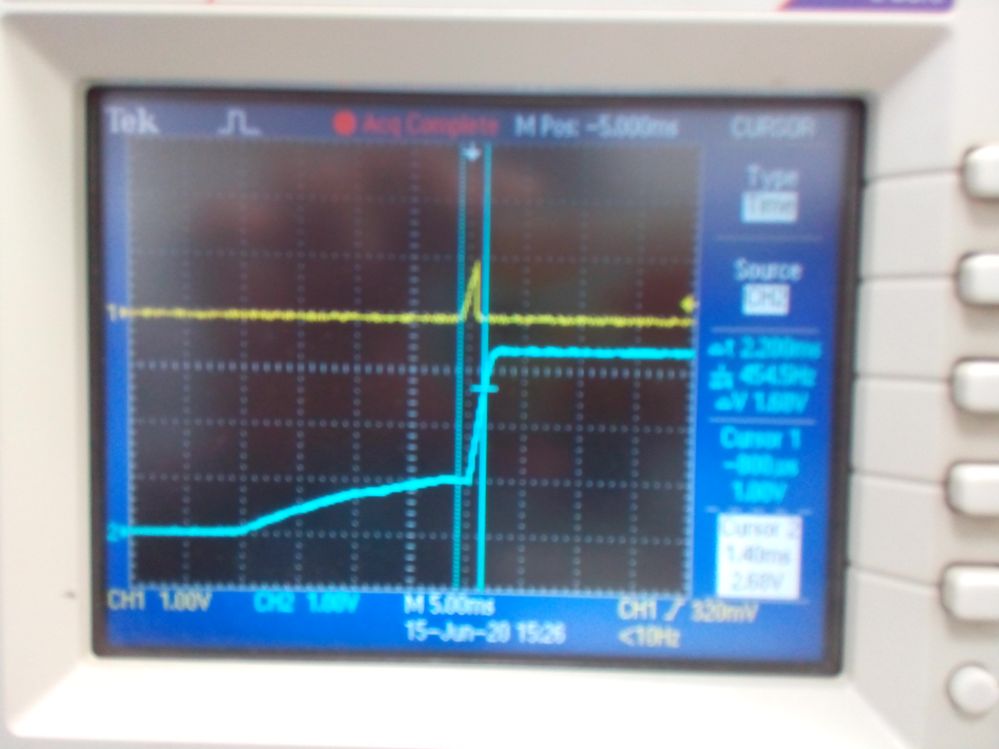

Sending the screenshot of the oscilloscope waveforms as attachment. The waveforms has 4 signals on the screen

1. 1st signal (yellow colour) is for POreset. Poreset is pulled low at the startup. After 2 seconds the POreset is made high. Before POreset is pulled high all the power supplies including the Processor core and IO supplies are high.

2. 2nd signal (green) is for Processor core which takes around 38ms.

3. 3rd signal (blue) is 1.35V

4. 4th signal (pink) is 1.8V

--

Regards

Abhijit Pethkar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In the QorIQ T2081 Data Sheet, 3.2 Power sequencing it is written:

"All supplies must be at their stable values within 400 ms."

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

As per the reference module page 223, DUART module works on platform clock/2 Frequency. But whenever the CPU frequency is changed on the console we are observing that the UART interface data rate is also changing. What is the relation between the CPU core clock frequency with the UART module?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please use debugger and check UART UDLB and UDMB values in proper and failing cases.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Fedor,

I had checked some of the on board voltages. Can you let me know whether the ripple and rise time that I have given below are correct

1. 1.8V (On board measured ripple 40mV and rise time of 2.8ms)

2. 1V (On board measured ripple 38.4mV and rise time of 1.6282ms)

3. 1.35V (On board measured ripple 28mV and rise time of 1.651ms)

4. 1.025V Core Voltage (On board measured ripple 21.6mV and rise time 2.005ms)

I had gone through the datasheet of T2081 and there is no power supply sequencing. Is there any power supply architecture specific to T2081 available? I was referring the T2080 evaluation module where Infineon power supply regulators are used. All the regulators have already reached EoL. Can you suggest any other regulators which are still in production for all the power supplies?

Also can you once review our design and let us know if because of design issue or layout issue we are finding the current issues cropping on the boards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Power sequencing: QorIQ T2081 Data Sheet, 3.2 Power sequencing

There are no specific recommendations for the EOL power supplies because these are not NXP parts.

Design review is possible by request of a FAE.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Fedor,

I have captured the rise time waveform of some on the board voltages. Can you let me know if they are correct?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

What are these voltages?

There are no notes.

To check ramp rate it is reasonable to use 1 ms time resolution.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

How many boards were tested?