- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- Sensors

- :

- Re: Component and via clearance around Freescale QFN packages

Component and via clearance around Freescale QFN packages

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Component and via clearance around Freescale QFN packages

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

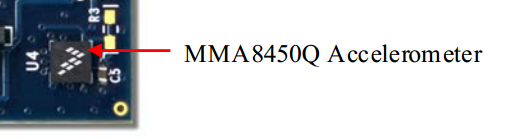

We are using a Freescale MMA8452Q accelerometer in our design. The layout guidelines (AN4077) have the following recommendations that I would like clarification on:

- Do not place any components or vias at a distance less than 5 mm from the package land area. This may cause additional package stress if it is too close to the package land area.

- Signal traces connected to pads are as symmetric as possible. Put dummy traces on NC pads in order to have same length of exposed trace for all pads.

In the same application guide is a photo of the Freescale demo board which appears to violate these recommendations having vias immediately around the package as well as a decoupling capacitor:

My question is - how essential is the clearance for vias and components to the MMA8452Q? Ideally I would like the decoupling closer than 5mm to the device. Also what is the mechanism for 'causing package stress' if a capacitor is within 5mm of the QFN?

Also, do I really need to put dummy traces on the NC pads?

Thanks, Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

This device is sensitive to board mounting, the mentioned recommendations were developed to minimize the offset errors, however, these are not critical.

You can place decoupling capacitor closer than 5mm to the device without a problem, under normal conditions, this should not cause any package stress.

And no, you do not really have to put dummy traces on the NC pads.

Regards,

Jose

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply. I will move my decoupling closer to the IC now.

You mentioned 'offset errors' - what do you mean by this?

Thanks, Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

One of the leading sources of error in an accelerometer is attributed to the 0g-offset or bias error, which is defined as “the difference between the measured value of the sensor from the true zero value”, this is what I meant with “offset error”.

You can find how to deal or calibrate this offset error in the following application note: http://cache.freescale.com/files/sensors/doc/app_note/AN4069.pdf

Regards,

Jose