- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

S32K312 HSE ABSWAP BOOT_SEQ Write FAIL

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

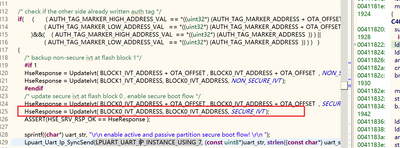

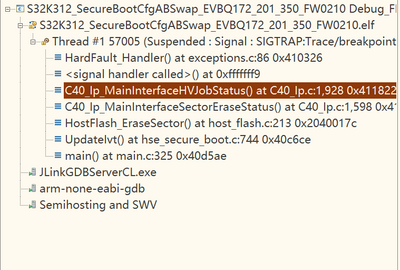

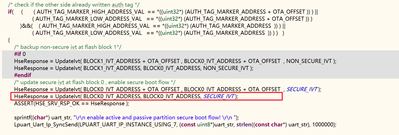

S32K312 HSE AB SWAP function, HARD_FAULT problem caused by failure to write Active area IVT BOOT_SEQ after all AB partition TAG writes are complete。

S32K312 HSE FW Version:HSE_FW_S32K312_0_2_40_0

S32K312 RTD Version:PlatformSDK_S32K3_2022_03 v2.0.3

HSE LIB Version:HSE_LIB_0.1.1.0.2

HSW FW INTERFACE:HSE_FW_S32K312_0_2_40_0\hse_ab_swap

Demo Project:

S32K312_SecureBootAppABSwap_EVBQ172_201_350_FW0210

S32K312_SecureBootCfgABSwap_EVBQ172_201_350_FW0210

Error Position:

In addition, I found that using JLINK single-step debugging, delay and wait for a while, can be configured successfully, running at full speed will certainly trigger the Hard Fault!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @liangyouchao,

Follow to the Release Note of the S32K3 RTD 2.0.3 package:

This release was developed on S32K3 parts (for packages refer to chapter 2.3 Supported

Derivatives) and tested on:

HSE firmware release: S32K312: HSE_0.2.6.0 (RTM)

Silicon P32K312NHVPBS 0P09C CTZM2132A.

If you are using S32K3 RTD 2.0.3 package with S32K312 and Crypto driver, you have to use correct "HSW FW" and the silicon chip as above. If not, we are not in charge of any issues will occur.

Best regards,

Dan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, sorry for the late reply, been busy with other things for a while now.

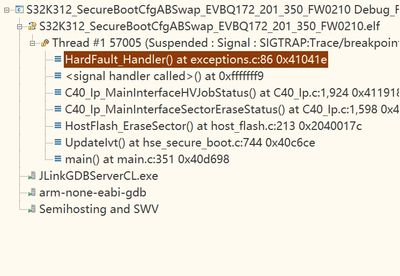

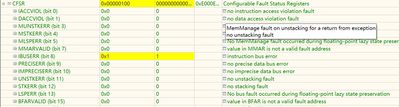

I followed your tips and changed the version of HSE FW to HSE_0.2.6.0, but I still have the above problem, I troubleshooted the cause of the hardware failure and found that the register bit is IBUSERROR, may I ask what is causing this problem.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @liangyouchao,

I got your issue from my side when I debug with T32 debugger.

I guess that most likely the code of UpdateIvt() function was placed on the Flash memory was erased when you call UpdateIvt( BLOCK0_IVT_ADDRESS, BLOCK0_IVT_ADDRESS, SECURE_IVT ); and after that, this cause the hardfault.

From my point of view, to avoid code of this function will be deleted, you can try to put the UpdateIvt() on the other address on Flash or put it on the SRAM for execution.

Best regards,

Dan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

```

write_status = HostFlash_EraseByLen(BLOCK0_IVT_ADDRESS , 0x2000);

```

but after I removed JLINK, I found other problems, and the line of code was not executable again when I didn't use JLINK emulation. Is there a problem why the configuration related to C40_RAM_CODE_ENABLE is not carried over to be used in subsequent versions?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @liangyouchao,

Which are the C40_Ip functions put on RAM? And how did you do that?

Best regards,

Dan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I referenced the configuration macros in C40_Ip in RTD version 1.0.0HF01 for the C40 running in RAM:

C40_RAM_CODE_ENABLE.

```

#if ( 1 == C40_RAM_CODE_ENABLE )

/* ram code start */

#define FLS_STOP_SEC_CODE

#include "Fls_MemMap.h"

#define FLS_START_SEC_RAMCODE

#include "Fls_MemMap.h"

#endif

```

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @liangyouchao :

我用s32k312做secure boot,遇到了和您一样的情况,请问您现在解决这个问题了吗?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @liangyouchao,

I can't find out "C40_RAM_CODE_ENABLE" in SW32K3_RTD_4.4_1.0.0, SW32K3_RTD_4.4_1.0.0_HF01 and SW32K3_RTD_4.4_1.0.0_HF02.

About your issue, most likely when you debug the C40_Ip functions can be placed on SRAM. But when you run (not debug) most likely those functions were not placed on SRAM.

Best regards,

Dan