- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

In LEGACY RX FIFO mode using FLEXCAN, is there no storage depth for the hardware?

If you have a storage depth, such as the 16 Rx FIFO Filters I use here, which take up 10 mailboxes, you can add 16 filters. But I only have FlexCAN_Ip_RxFifo(INST_FLEXCAN_0,&Rxbuf) in the interrupt; This function can read FIFO values under CAN0. If my CAN interrupt priority is low, how can I read other frames stored in the FIFO? In addition, why do these 10 mailboxes also need to set masks?

I want to implement CAN frames CAN be saved in the mailbox, at a low CAN priority, or use a query to read CAN frames, and ensure that no frames are lost.

I see in the routine what seems to be a software-implemented FIFO, which is not what I want.

Or I might as well use the standard mail function and set up a few more mailboxes that match the ID that receives the most frequently.

Or do you use FIFO and open DMA?

已解决! 转到解答。

Hi,

legacy RXFIFO can hold up to 6 messages without CPU intervention, if more messages comes it can be lost if RXFIFO is not read out in time. RTD driver is written in a way you need to call FlexCAN_Ip_RxFifo first, an interrupt is called once there is at least 1 message in the RXFIFO, driver reads single message from RXFIFO and user have to call FlexCAN_Ip_RxFifo again to enable interrupt again. Similar operation is done if DMA mode is selected, still FlexCAN_Ip_RxFifo must be called to get a data.

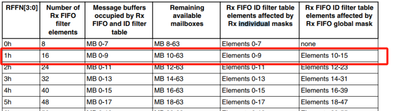

If 16 filter elements are selected, first 10 elements use first 10 individual mask acceptance registers to provide acceptance mask (assuming individual masking scheme is selected).

Beside RXFIFO you can use rest of available MBs for TX or RX functionality.

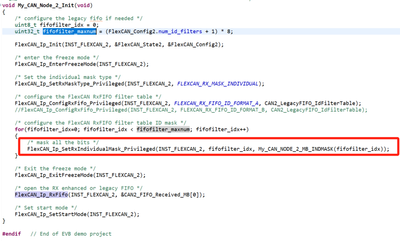

You can refer to below example ...

https://community.nxp.com/t5/S32K-Knowledge-Base/Example-S32K312-CAN-Transmit-amp-Receive-Using-MB-a...

BR, Petr

Hi,

legacy RXFIFO can hold up to 6 messages without CPU intervention, if more messages comes it can be lost if RXFIFO is not read out in time. RTD driver is written in a way you need to call FlexCAN_Ip_RxFifo first, an interrupt is called once there is at least 1 message in the RXFIFO, driver reads single message from RXFIFO and user have to call FlexCAN_Ip_RxFifo again to enable interrupt again. Similar operation is done if DMA mode is selected, still FlexCAN_Ip_RxFifo must be called to get a data.

If 16 filter elements are selected, first 10 elements use first 10 individual mask acceptance registers to provide acceptance mask (assuming individual masking scheme is selected).

Beside RXFIFO you can use rest of available MBs for TX or RX functionality.

You can refer to below example ...

https://community.nxp.com/t5/S32K-Knowledge-Base/Example-S32K312-CAN-Transmit-amp-Receive-Using-MB-a...

BR, Petr

CAN I understand that I first call this function once during initialization, so if I have a message I will enter the interrupt, and if there are more than two messages, I will immediately enter the CAN interrupt again after reading the message for the first time and exiting the interrupt?