- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

S32K148 FlexNvM with EEPROM and RTD

Hi!

I am currently using an UART bootloader which is based on the bootloader described at AN12218.

After the timeout this bootloader starts my application which has an offset of 0x1000 at the P-Flash.

The application is using the RTD 1.0.0 framework.

The bootloader is located at the start of the FlexNVM (0x1000 0000).

This configuration works fine until now.

Now I want to use the last 64K of the FlexNVM as my EEEPROM, as described in AN11983.

Based on the EEp_Ftfc_lp_Example_S32K148 I partitioned my NVRAM for this configuration (at least I think I did

/* partition for EERAM 64K with NOT loading EERAM at reset in hardware */

TestEep_FlexNvmProgramPartCmd(EEP_FTFC_KEY_SIZE_0_BYTES, EEP_FTFC_VERIFY_ONLY_DISABLED, \

EEP_FTFC_LOAD_AT_RESET_ENABLED, EEP_FTFC_EERAM_SIZE_4K, T_EEP_SIZE);I am aware the any data in the NVRAM is erased after the partitioning is done.

So I downloaded the example mentioned above for the partitioning and then downloaded my bootloader and application again after the partitioning.

But now neither the bootloader nor the application is starting up again, until I am deleting the whole chip again and download the whole system without the partitioning.

What am I doing wrong?

Regards Christof

Hi, sry for jumping into this thread.

I'm working with S32K116 on quite same subjet, and i think you can answer my questions.

i also want to use partitionned FlexNVM as (for K116) : 8KB DFlash and 24KB EEProm.

Can you confirm that:

- I shall add FTFC_IP AND FTCF_EEP_IP in the driver part of configuration tool

- i shall write FlexNVM partitionning activities by myself

Maybe i'm missing something but, from the last point, I really don't understand why this activitie is not managed by none of these drivers...

Thanks in advance for you help

Francois.

Hi @christofhaiding,

That requires some debugging on your side.

You wrote: "now neither the bootloader nor the application is starting up again", but what does it mean?

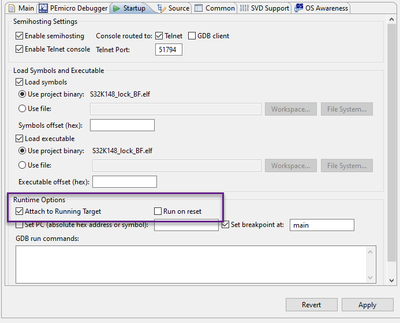

Can you attached the debugger to the running target (without resetting it) and check where it is stuck?

Can you scope the reset_b pin? Is the MCU resetting itself?

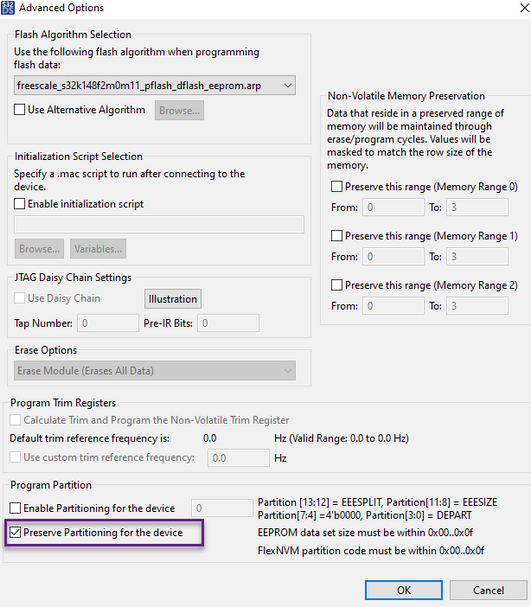

Do you preserve the partitioning when you are loading the bootloader.

Can you read the FCFG1_DEPART register to double-check the partitioning?

BR, Daniel

Hi Daniel!

Thanks for the reply.

First of all, may I ask you where these screenshots are from?

I am using the J-Link Segger Debugger.

So I can't find the settings at the debugger and the advanced settings.

With the phrase: "now neither the bootloader nor the application is starting up again" I mean that the whole system stalls.

Except if I am downloading the application throught the debugger.

But I already managed to get the system booting again, by setting the parameter "EEP_FTFC_LOAD_AT_RESET_DISABLED" instead of "EEP_FTFC_LOAD_AT_RESET_ENABLED".

Regards

Christof

Hi Christof,

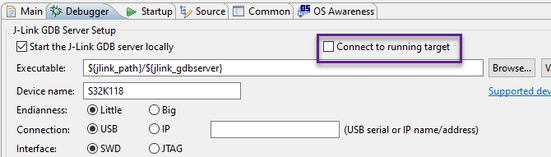

The screenshots show configuration of the PE Micro plugin in the S32DS IDE.

The SEGGER plugin does not have an option to preserve the partitioning.

There is an option to connect the debugger to a running target though:

Anyway, can you put the code that partitions the MCU into the bootloader?

You can read the DEPART register in the bootloader's code

if(DEPART == 0xF){

// do partitioning

}

alse{

// already partitioned, skip partitioning

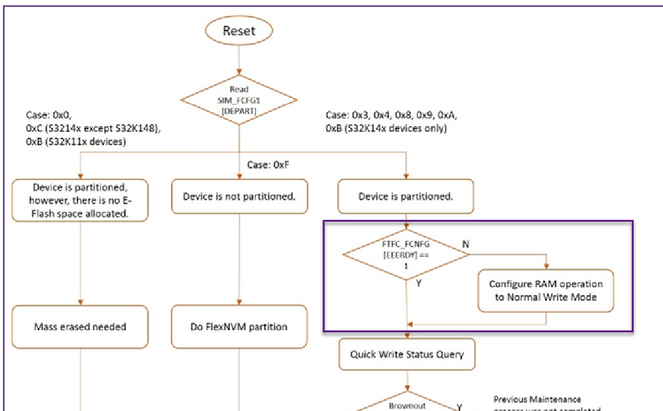

}With EEP_FTFC_LOAD_AT_RESET_DISABLED, the EEPROM will not be ready out-of-reset (EEERDY = 0, RAMRDY = 1).

The EEP_FTFC_LOAD_AT_RESET_ENABLED parameter enables Automatic EEPROM backup copy down during the reset sequence. It clears the CCIF flag until the EEPROM is ready (EEERDY = 1).

Can you make sure you don't launch any FTFC commands before EEERDY = 1 & CCIF = 1?

Thank you,

BR, Daniel

Hi Daniel!

Thanks for the Info.

But still if I set the EEP_FTFC_LOAD_AT_RESET_ENABLED option the bootloader will not start automatically.

Only if I download it via the Segger.

Is there something I have to change at the linker file?

Which are the disadvantages of setting the it to disabled?

Regards

Christof

Hi Christof,

Can you take a look at AN11983 Using the S32K1xx EEPROM Functionality

https://www.nxp.com/docs/en/application-note/AN11983.pdf

Figure 12. EEE initialization flow chart

If disabled, EEERDY = 0 out of reset. You would need to configure the FlexRAM in the code (Set FlexRAM FTFC command) to enable the EEPROM.

There is no need to modify the linker file.

BR, Daniel

Hi Daniel!

I just saw the setting of the FlexRam function is done at the function "Ftfc_Eep_Ip_Init"

if (0U == (IP_EEPROM->FCNFG & FCNFG_EEERDY_MASK))

{

/* When the memory partitioning is done without the option to load the EEPROM data

* to FLEXRAM at reset, a FLEXRAM_FCC_MODE_EEERAM_NORMAL command is needed (so EEERDy gets set).

* Also, the FLEXRAM_FCC_GET_FLEXRAM_STATUS cmd is not allowed unless the EEERDY bit is set. */

Status = Ftfc_Eep_Ip_CmdSetFlexramFunction(FLEXRAM_FCC_MODE_EEERAM_NORMAL, 0U);

}Which means setting up the EEPROM with the disabled option should be fine.

Am I right?

Regards

Christof

Yes, that is correct, it enables the EEEPROM - triggers the copy-down operation (From FlexNVM to FlexRAM).

The MCU can be either in reset (which can be monitored at the reset_b pin) or it is executing code.

There is no other option.

If you see the reset_b signal being periodically driven LOW, then, you need to find the source of the reset (RCM_SRS).

If, however, the MCU is not in reset, and the application does not work as it should, the execution is probably stuck in a loop.

You need to connect the debugger to the running target, then halt the execution and check where it is stuck.

But since the issue is with the EEPROM being enabled right out-of-reset, I guess there must be some issues with the FTFC controller. Because as I said, the CCIF flag gets cleared, and the code should wait until CCIF = 1 again.

Regards,

Daniel

Hi!

Thanks for the description.

I will have a look at the options you suggested.

Regards

Christof

Hi Daniel!

Thanks for the Information.

But still I have the problem that no code is executed after setting the enabled options.

Thats my main problem.

Regards

Christof