- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

S32K144 and SBC(MC33FS6500) SPI CS Problem

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi folks,

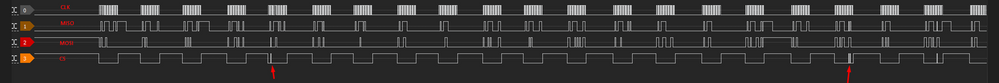

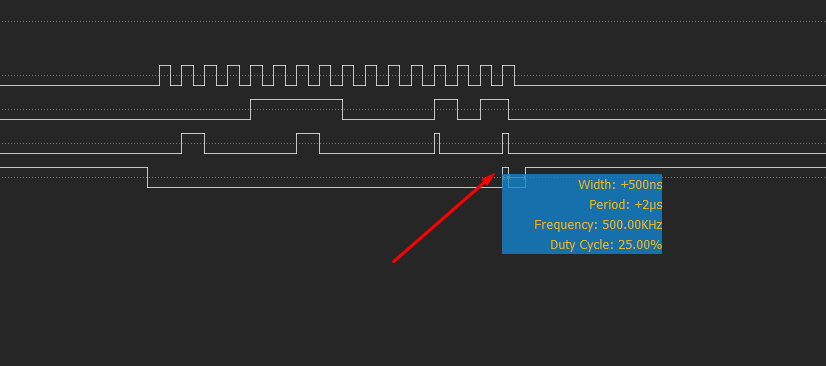

When communicating SPI between S32k144 and SBC (MC33FS6500), I see that the Chip Select pin is unexpectedly pulled to high while the message transmission is still in progress.

What can I do ?

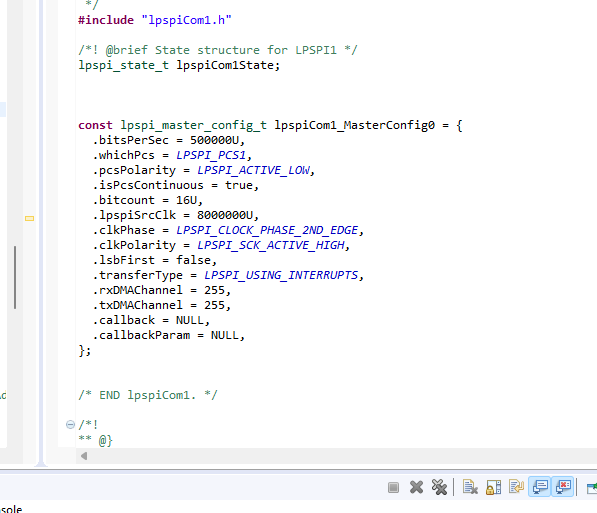

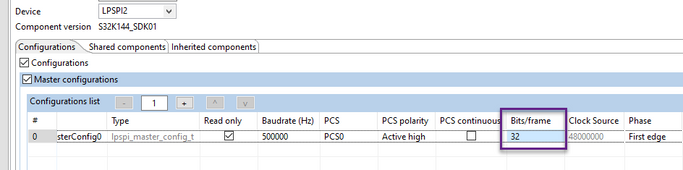

My SPI config

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @danielmartynek ,

As you seen, 16 clock cycle ,16 bit

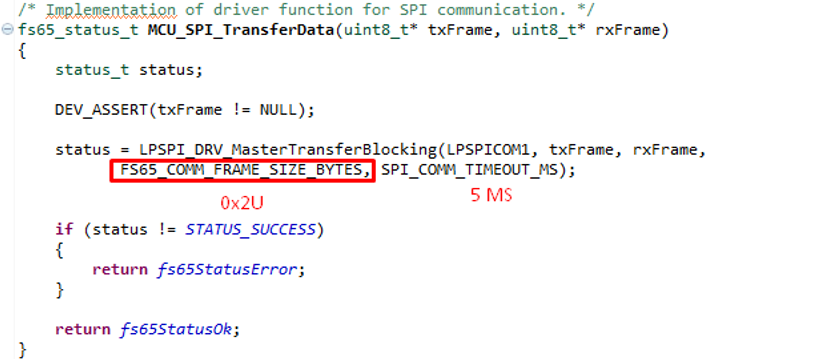

This is transfer function

I changed the bitcount to 32, nothing changed.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Did you really change the bitcount in the configuration of the driver?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @danielmartynek ,

Our main problem is related to CS pin state inconsistency .

We have to use 16 bit frame format in order to communicate our sensor(FS65xx) . But Sometimes CS pin logic level changed without any reason(as you seen above pictures).

What cause this problem? How can we eliminate this CS select inconsistency

Best regards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @engineer_attila,

I'm sorry, I misread the issue.

In this case, can you measure the bus with an analog oscilloscope?

This digital signal does not tell whether the signal goes all the way to VDD or if it is just a glitch.

Does it happen always at the time MOSI is HIGH?

Thanks,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @danielmartynek ,

Most of the times it occurs during when MOSI was HIGH,

But sometimes this CS problem not seen alongs with transmission.

I'm curious , is it related to MOSI?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

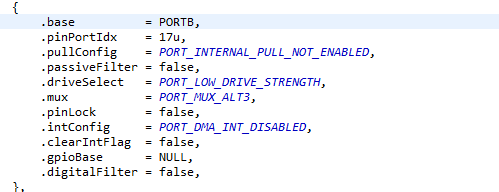

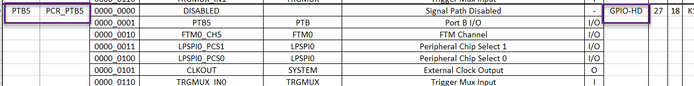

Hi @engineer_attila,

Which pin do you use for the CS?

If the pin has the High-drive capability (GPIO-HD), is the the PCR[DSE] bit of the pin set?

Thanks,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

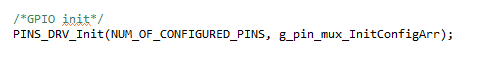

This PTB17 does not have the GPIO-HD function.

Can you use different PCS?

Like PTB5

Have you been able to measure the signal with an analog osciloscope?

Can you decrease the bitrate?

Thanks,

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @danielmartynek ,

Sorry for late response. My colleagues will change the CS pin to GPIO-HD for next revision.

I'm curious what is the equivalent of GPIO-HD pins for MPC5775 series?

Best regards.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @engineer_attila,

Did you get rid of the glitches with this configuration? How does it look at an analog osciloscope?

I'm not familiar with the MPC5775 series, but I see there is a similar option in the PCR[SRC] register.

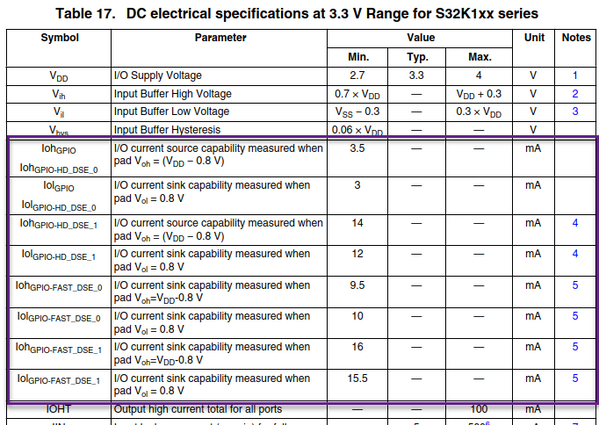

On S32K1xx, the GPIO-HD pins with PCR[DSE] = 1 have higher current capabilities and are faster.

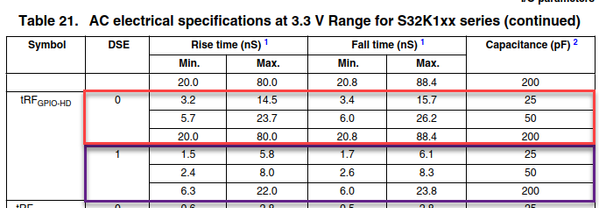

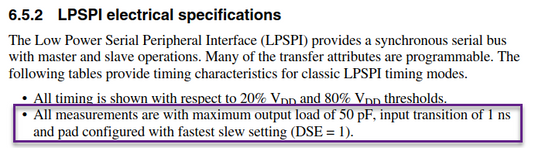

Also, the whole LPSPI specification in the DS was taken at GPIO-HD pins (DSE = 1):

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @engineer_attila,

How long the transfer should be?

Can you show how you call the transfer function?

You could increase the .bitcount to 32, for example.

Regards,

Daniel