- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K144: If 'Cache Enable' have an effect on 'driver Interrupt'

S32K144: If 'Cache Enable' have an effect on 'driver Interrupt'

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K144: If 'Cache Enable' have an effect on 'driver Interrupt'

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

In my project,I found that:

when I operate 'erase flash' or 'write flash' , syetem will reset,

therefore,I add sentence in main() as below(founded in cookbook) and system working normally:

LMEM->PCCCR = LMEM_PCCCR_INVW0(1) | LMEM_PCCCR_INVW1(1) | LMEM_PCCCR_GO(1) | LMEM_PCCCR_ENCACHE(1);

but this sentence maybe have an effect on driver - interrupt(such as SPI,UART,etc.)

for example:

Before: I set UART(460800,int-priority-5)/SPI0(10M,int-priority-5)/SPI1(10M,int-priority-5) and system working normally

After:I have to set UART(460800,int-priority-5)/SPI0(1M,int-priority-7) SPI0(1M,int-priority-7)

If I don't set like After , interrupt maybe working weirdly(eg. data missing sometimes) ,I have to modify priority and cut down SPI-bautrate to guarantee data-completeness,

Dose anyone know this?

If anyone has any idea,please share with me ,thanks very very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello langweihua1643@163.com,

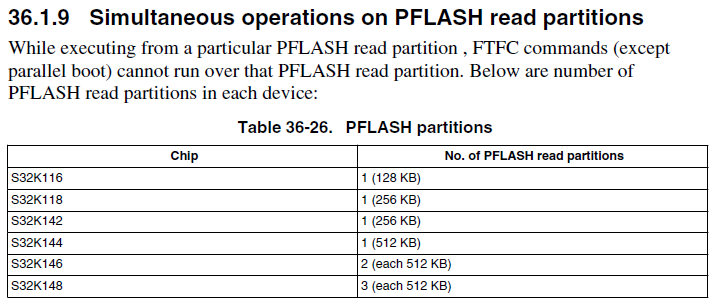

Regarding the reset, you probably launch the PFlash FTFC commands from the PFlash partition (there is only one PFlash partition on S32K144).

You need to execute the code that launches the FTFC commands (clear CCIF, wait until CCIF = 1) from a different flash partition (DFlash on S32K144) or SRAM.

Do you invalidate the Cache after the FTTC programming/erasing?

Regards,

Daniel