- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K can't wake up from VLPS occasionally

S32K can't wake up from VLPS occasionally

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

i"m using the s32k142 with RUN mode and VLPS mode, through the GPIO interrupt to wake up the chip from VLPS mode, it's working fine in most of times,but there is a slight chance that can't wake up from VLPS mode,only reconnect the power can make chip normal.this situation happened in different boards and can't reproduce.

I would like to know,what situation may cause the MCU can't wake up from VLPS mode? thank you very much.

BR

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

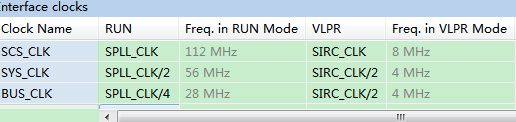

Could you please make sure that PREDIV_SYS_CLK frequency / BUS_CLK frequency configuration for RUN/VLPR mode is greater than or equal to 2 before executing the transition to VLPS.

Mask Set Errata for Mask 0N33V

https://www.nxp.com/docs/en/errata/S32K142_0N33V.pdf

ERR011063

Thank you,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please make sure that the interrupts are not masked when the MCU enters VLPS.

You could try using the highest interrupt priority only for the interrupts that are used to wake the MCU up.

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

we enabled the PORTB interrupts before enters VLPS, the wake up source was connected with PTB ,the priority was highest.

and , it can wake up normally at the most of times,just 2 or 3 times dead in VLPS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you please make sure that PREDIV_SYS_CLK frequency / BUS_CLK frequency configuration for RUN/VLPR mode is greater than or equal to 2 before executing the transition to VLPS.

Mask Set Errata for Mask 0N33V

https://www.nxp.com/docs/en/errata/S32K142_0N33V.pdf

ERR011063

Thank you,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

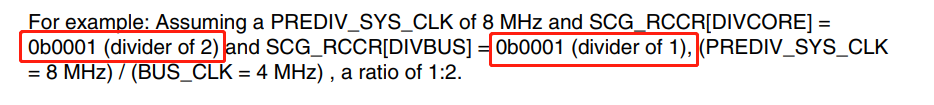

I checked my clock configuration and maybe it's the reason.

and I was wondering whether there should be some inconsistency about the data in the example. Based on the errata, the dividers in red circles should not be the same but parameters is the same.

thank you !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

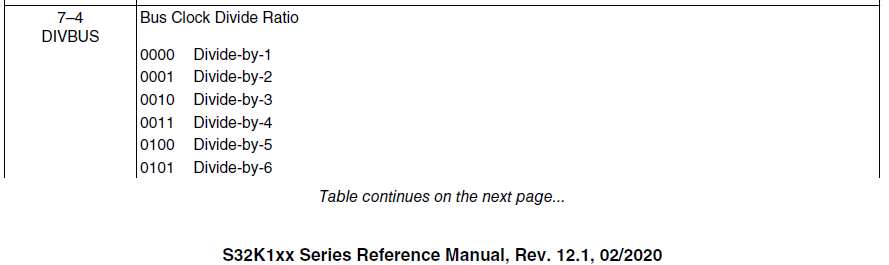

Yes, based on the RM, SCG_RCCR[DIVBUS] = 0b0001 divides the clock by 2.

Thank you for reporting it.

Regards,

Daniel