- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: How to block TXD via TXCTSE bit?

How to block TXD via TXCTSE bit?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

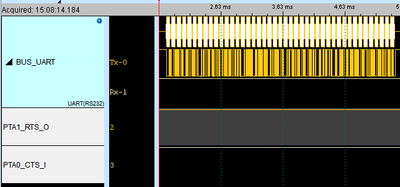

I'm using EVK S32K118-48 board

I want to use LPUART0 for hardware flow control,

and setting LPUART0 pinmux as follows,

PTA0 for LPUART0_CTS

PTA1 for LPUART0_RTS

PTA2 for LPUART0_RX

PTA3 for LPUART0_TX

MODIR register bit settings,

LPUART_MODIR_TXCTSSRC(0) : 0b - CTS input is the CTS_B pin.

LPUART_MODIR_TXCTSC(0) : 0b - CTS input is sampled at the start of each character.

LPUART_MODIR_TXCTSE(1) : 1b - Enables clear-to-send operation.

However, trying to use CTS to block TXD doesn't work.

Can you tell me how to make it work properly?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

you are right. Found a problem with my s32k118 evk board. I'll fix my board issues. Then close this question. Thanks.

Best Regards,

Alston

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

setting looks normal. Try to check port PDIR register if pin logic level is 1, which should pause transmitting.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Petr,

Thanks for your reply.

Let me describe it in more detail.

S32K118_IO_Signal_Description_Input_Multiplexing.xlsx :

| Port | CR | SSS | Function | Module | Description | Direction |

| PTA0 | PCR_PTA0 | 0000_0110 | LPUART0_CTS | LPUART0 | Clear To Send (bar) | I |

| PTA1 | PCR_PTA1 | 0000_0110 | LPUART0_RTS | LPUART0 | Request To Send | O |

| PTA2 | PCR_PTA2 | 0000_0110 | LPUART0_RX | LPUART0 | Receive | I |

| PTA3 | PCR_PTA3 | 0000_0110 | LPUART0_TX | LPUART0 | Transmit | I/O |

...

However, the signals I see are PTA0 as output and PTA1 as input.

LPUART0->MODIR = 0x00000009

PTA->PDIR = 0x0000002E

I set TXCTSE and control PTA1(CTS), but cannot mask the PTA3(TXD) signal.

Did I miss something?

BR, Alston

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Petr,

Thanks for your reply.

Your code works fine.

However, I tried modifying the PTB0/PTB1 pins to PTA3/PTA2

this will not work.

as follows

void PORT_init (void)

{

/*!

* Pins definitions

* ===================================================

*

* Pin number | Function

* ----------------- |------------------

* PTA2 | LPUART0 RX

* PTA3 | LPUART0 TX

*/

PCC->PCCn[PCC_PORTB_INDEX]|=PCC_PCCn_CGC_MASK; /* Enable clock for PORT B */

PCC->PCCn[PCC_PORTA_INDEX]|=PCC_PCCn_CGC_MASK; /* Enable clock for PORT B */

PORTA->PCR[0]|=PORT_PCR_MUX(6); /* Port A, bit 0, ALT=6: UART CTS. */

PORTA->PCR[2]|=PORT_PCR_MUX(6); /* Port A, bit 2, ALT=6: UART RX. */

PORTA->PCR[3]|=PORT_PCR_MUX(6); /* Port A, bit 3: ALT=6: UART TX. */

}

Can't PTA3/PTA2 pin be used for tx/rx?

Br, Alston

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

per IO signal table this setting would be possible, I do not expect issues here. Maybe check board schematic if signal can be measured and be on right header. But this looks normal too.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

you are right. Found a problem with my s32k118 evk board. I'll fix my board issues. Then close this question. Thanks.

Best Regards,

Alston