- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: How can the time for SPI transmission initiation be shortened?

How can the time for SPI transmission initiation be shortened?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How can the time for SPI transmission initiation be shortened?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I have some questions about S32K148 SPI using.

The SPI2 configuration is

/* SPI Master Configurations */

spi_master_t spi2_MasterConfig0 =

{

.baudRate = 4000000U,

.ssPolarity = SPI_ACTIVE_LOW,

.frameSize = 8,

.clockPhase = READ_ON_EVEN_EDGE,

.clockPolarity = SPI_ACTIVE_HIGH,

.bitOrder = SPI_TRANSFER_MSB_FIRST,

.transferType = SPI_USING_DMA,

.rxDMAChannel = 2U,

.txDMAChannel = 3U,

.callback = NULL,

.callbackParam = NULL,

.ssPin = 1,

.extension = NULL,

.isPcsContinuous = true,

.isMasterDevicesDelayed = false,

};

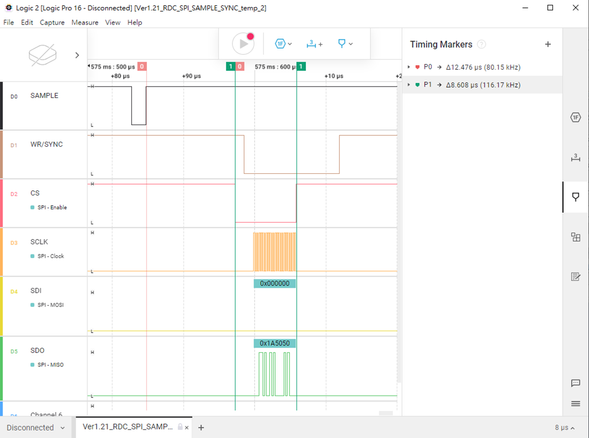

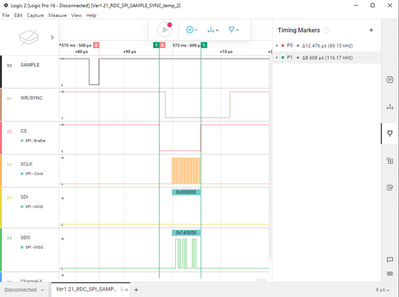

I aim to control the time required for transmitting 24 bits of SPI data to be under 10 us. However, I am currently facing challenges in reducing the duration between the SPI command and the CS (Chip Select) pin going LOW.

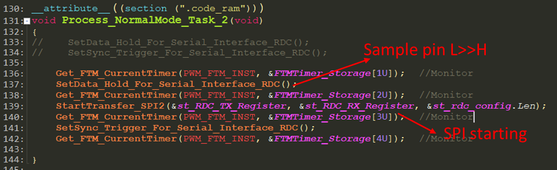

void StartTransfer_SPI2(void* u8_tx_buff, void* u8_rx_buff, void* u16_len)

{

SPI_MasterTransfer(&spi2Instance, u8_tx_buff, u8_rx_buff, *(uint16_t*)u16_len);

}

How could I reduce the P1 P0 time for waiting the SPI Starting.

Regards,

Leon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Leon06,

What drivers / version do you use?

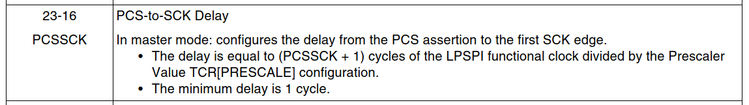

Can you read the LPSPI_CCR[PCSSCK] register?

Thank you,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Leon06,

CCR = 0x00140000, PCSSCK = 0x14

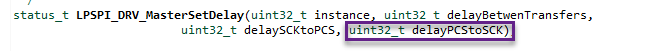

Use this function to set a shorter delay:

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

I am sorry. I am asking for reducing P0 not P1. P0 is the time between SPI starting transmission intimation and before the CS being low.

Leon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Leon06,

The delay is caused by the overhead of the application SW and the LPSPI SDK driver.

You can either increase the system clock frequency or reduce the amount of code between Sample and CS assertion, for example by using you own code to drive the LPSPI.

https://www.nxp.com/docs/en/application-note/AN5413.pdf

AN5413SW

https://www.nxp.com/webapp/Download?colCode=AN5413SW&docLang=en

Regards,

Daniel