- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Software Forums

- :

- S32 SDK

- :

- Re: What if the CAN message buffer is less than the tx and rx CAN message id?

What if the CAN message buffer is less than the tx and rx CAN message id?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I use S32DS forARM.2018.R1 and SDK RTM2.0.0.

In FlexCAN,

Could not have more message buffers?

What if the message buffer is less than the tx and rx message id?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kim,

Could not have more message buffers?

Every FLEXCAN Interface have a fixed no of message buffers MBs (Hardware dependent).

You can use more FLEXCAN interfaces if you need more message buffers and the application handle them ! be aware that the drivers use nested interrupts and all instances will have the same priority. And different interfaces have different CAN features support (CAN FD, PNET, no of MBs).

What if the message buffer is less than the tx and rx message id?

The MB Index is not dependent of the Message ID (this can be configured individual for Rx MB\ Tx MB, or as an acceptance mask \ individual filter for Rx FIFO Mode).

Please provide more details about what you want to do so I can give you specific advice, and what chip you use and development board (custom or devkit).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kim,

Could not have more message buffers?

Every FLEXCAN Interface have a fixed no of message buffers MBs (Hardware dependent).

You can use more FLEXCAN interfaces if you need more message buffers and the application handle them ! be aware that the drivers use nested interrupts and all instances will have the same priority. And different interfaces have different CAN features support (CAN FD, PNET, no of MBs).

What if the message buffer is less than the tx and rx message id?

The MB Index is not dependent of the Message ID (this can be configured individual for Rx MB\ Tx MB, or as an acceptance mask \ individual filter for Rx FIFO Mode).

Please provide more details about what you want to do so I can give you specific advice, and what chip you use and development board (custom or devkit).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nan,

I develop on custom board and reference board is S32K144 EVB.

I Handle 32 CAN ID.

I set message box each ID.

I don't use FIFO.

/* Set RX Message Box */ /* 0 ~ 7 */

for(lU8Idx = 0 ; lU8Idx < SRVCANHS_RX_MSG_MAX ; lU8Idx++)

{

lU8RxMbIdx = SRVCANHS_CONVERT_RXIDX_TO_MBIDX(lU8Idx);

/* Set TX Message Box */ /* 8 ~ 32 */

for(lU8Idx = 0 ; lU8Idx < SRVCANHS_TX_MSG_MAX ; lU8Idx++)

{

DRVIF_CANHS_CONFIG_TX_MB(lU8Idx, &gStSrvCanHsTxMsgTable[lU8Idx].dataInfo, gStSrvCanHsTxMsgTable[lU8Idx].canId);

}

Could you provice the example code with FIFO?

Thanks and best regards,

Byungju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can find a sample code for fifo configuration in this thread CAN FLEXCAN_EVENT_RX_COMPLETE interrupt issue

There is a post of mine that configure the RXFIFO mode and filters to accept any ID message, if you configure CAN_SetRxFilter to mach with your filter mask and than to accept only the IDs you require.

The example there it use CAN_PAL driver.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Nan,

I use FLEXCAN . not CAN_PAL.

If you don't mind, I want to get FLEXCAN example code.

I want know the way that one mail box receive multiple CAN ID.

Thanks and best regards,

Byungju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Byungju,

First of all I suggest to take the last SDK available for S32K144 which is S32 SDK K1xx BETA 2.9.0 can be found here S32 Design Studio for ARM 2018.R1 - Update 7 available .

An exemple of RX fifo use to receive multiple IDs on the same MBs (The fifo use MB0 to MB6 to store messages). this example use extended ID filters, you can adapt to use standard IDs if you need by setting filters type extended as false flTable[i].isExtendedFrame = false; and the mask type on the FLEXCAN_DRV_SetRxIndividualMask and FLEXCAN_DRV_SetRxFifoGlobalMask;

const flexcan_user_config_t canCom1_InitConfig0 = {

.fd_enable = false,

.pe_clock = FLEXCAN_CLK_SOURCE_OSC,

.max_num_mb = 32,

.num_id_filters = FLEXCAN_RX_FIFO_ID_FILTERS_8,

.is_rx_fifo_needed = true,

.flexcanMode = FLEXCAN_NORMAL_MODE,

.payload = FLEXCAN_PAYLOAD_SIZE_8,

.bitrate = {

.propSeg = 7,

.phaseSeg1 = 4,

.phaseSeg2 = 1,

.preDivider = 0,

.rJumpwidth = 1

},

.bitrate_cbt = {

.propSeg = 7,

.phaseSeg1 = 4,

.phaseSeg2 = 1,

.preDivider = 0,

.rJumpwidth = 1

},

.transfer_type = FLEXCAN_RXFIFO_USING_INTERRUPTS,

.rxFifoDMAChannel = 0U

};

#define TX_MAILBOX (1UL)

#define TX_MSG_ID (1UL)

/* The MB0 represents the fifo MB to extract the messages received by RxFIFO */

#define RX_MAILBOX (0UL)

#define RX_MSG_ID (2UL)

main()

{

flexcan_id_table_t flTable[10];

status_t status;

for(i=0;i<10;i++)

{

flTable[i].id=i;

flTable[i].isExtendedFrame=true;

flTable[i].isRemoteFrame=false;

}

status = FLEXCAN_DRV_Init(INST_CANCOM1, &canCom1_State, &canCom1_InitConfig0);

/* Need to provide a no of ID filters based on .num_id_filters = FLEXCAN_RX_FIFO_ID_FILTERS_8, from configuration structure canCom1_InitConfig0 */

FLEXCAN_DRV_ConfigRxFifo(INST_CANCOM1,FLEXCAN_RX_FIFO_ID_FORMAT_A,&flTable);

/* Bit 31 from the mask it represents the remote flag acceptance ! */

FLEXCAN_DRV_SetRxFifoGlobalMask(INST_CANCOM1, FLEXCAN_MSG_ID_EXT, ((1U<<31U)|0x1FFFF));

for(i=0; i<22; i++)

{

status = FLEXCAN_DRV_SetRxIndividualMask(INST_CANCOM1,FLEXCAN_MSG_ID_EXT, i, ((1U<<31U)|0x1FFFF));

if(status == STATUS_CAN_BUFF_OUT_OF_RANGE )

break;

}

while(1)

{

/* Define receive buffer */

flexcan_msgbuff_t recvBuff;

/* Start receiving data in RX_MAILBOX. */

FLEXCAN_DRV_RxFifo(INST_CANCOM1, &recvBuff);

/* Wait until the previous FlexCAN receive is completed */

while(FLEXCAN_DRV_GetTransferStatus(INST_CANCOM1, RX_MAILBOX) == STATUS_BUSY);

}

}

BR,

Alexandru Nan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Nan,

Thanks for your help.

I confirm the RX FIFO function.

But Tx function does not work.

When I send the CAN message with mail box index '0', FLEXCAN_DRV_Send function return STATUS_BUSY '0x002'.

When I send the CAN message with mail box index '1', FLEXCAN_DRV_Send function return STATUS_CAN_BUFF_OUT_OF_RANGE '0x300'.

How to resolve it?

How to know which mail box index is for RX FIFO?

My send code is below.

/**********************************************************************************************************************/

void SrvCanHsSendData(uint32 iU32Mailbox, uint32 iU32Id, uint8* ipU8Data, uint32 iU32Len)

{

status_t result = STATUS_SUCCESS;

/* Set information about the data to be sent

* - 1 byte in length

* - Standard message ID

* - Bit rate switch enabled to use a different bitrate for the data segment

* - Flexible data rate enabled

* - Use zeros for FD padding

*/

flexcan_data_info_t dataInfo =

{

.data_length = iU32Len,

.msg_id_type = FLEXCAN_MSG_ID_STD,

.enable_brs = true,

.fd_enable = false,

.fd_padding = 0U,

.is_remote = false

};

/* Configure TX message buffer with index TX_MSG_ID and TX_MAILBOX*/

FLEXCAN_DRV_ConfigTxMb(iU32Mailbox, &dataInfo, iU32Id);

/* Execute send non-blocking */

result = FLEXCAN_DRV_Send(iU32Mailbox, &dataInfo, iU32Id, ipU8Data);

printf("[SRV_CANHS] TX result : %X\n", result);

}

/**********************************************************************************************************************/

Please let me know.

Thanks and best regards,

Byungju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

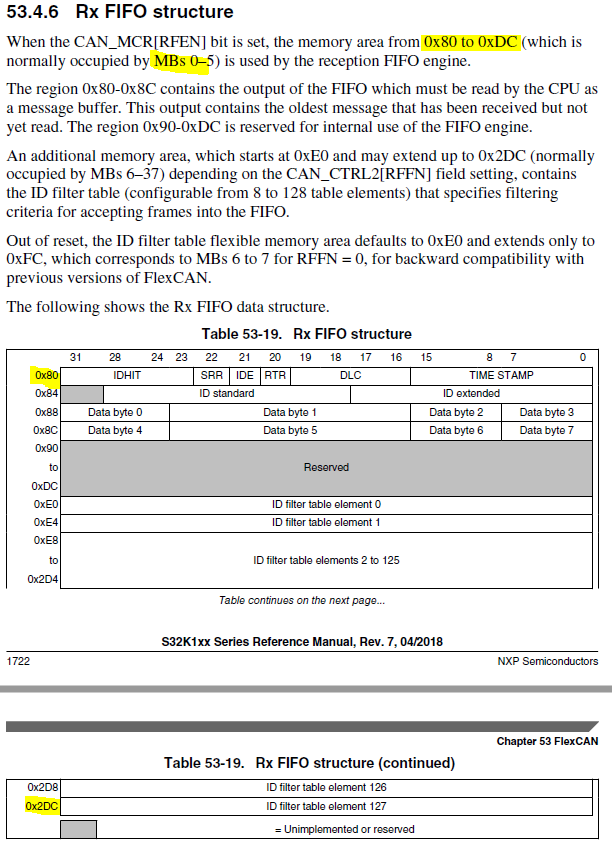

Simple by reading carefully what I previous said "The fifo use MB0 to MB6 to store messages" So mb_idx 0-5 are not used in process of tx are exclusively in rx. the mb1 to mb5 can be used in some conditions as tx but I don't recommend it and the driver wasn't designed to be allowed. After the receiving MBs are the FilterID space occupied based on how many you have configured in your case will be 6-7Mbs so next available MB will be 8 that can be used in TX. For this infos read the RM for the chip on the FLexCAN peripheral will find the message buffer structure to understand how the things work. And which filters are affected by individual or global mask based on numbers of filter configured you will find a table under RFFN bitfield of CAN_CTRL2 register in RM.

You receive MB0 busy because all time is used in RX fifo and is armed for receiving, and MB1 actual will try to set next a mb designed to be used by RxFIFO and for this you will get out_of range status.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Nan

Thanks for your support.

I use 32 RX ID.

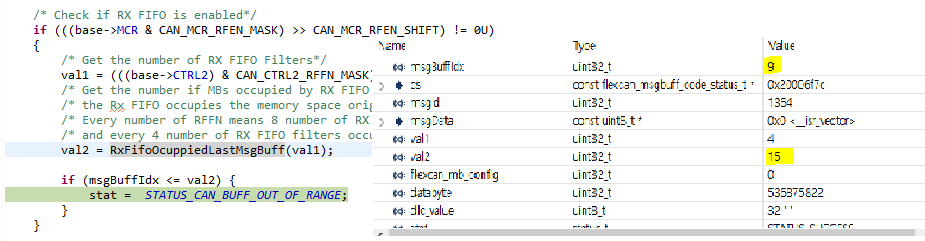

In my code, MB7 ~ MB15 return STATUS_CAN_BUFF_OUT_OF_RANGE '0x300'.

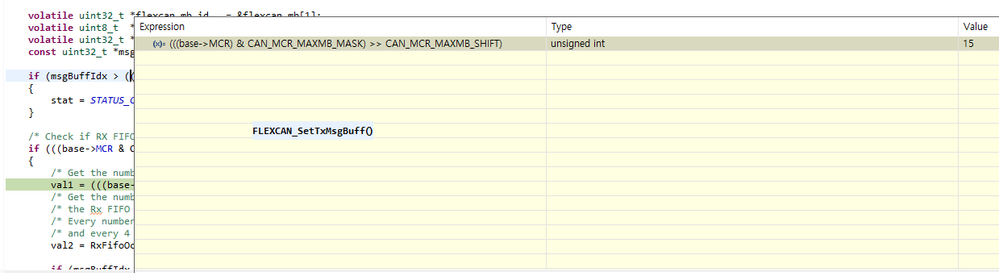

Return function and point is below.

Please check it and let me know how to resolve it.

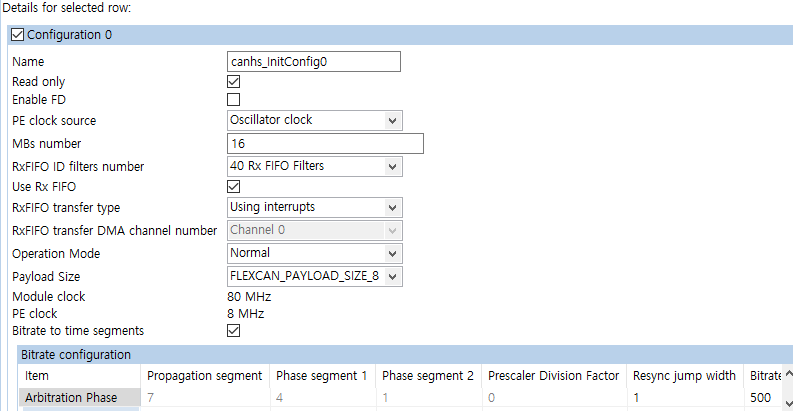

- CAN configuration

Thanks and besr regards,

Byungju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

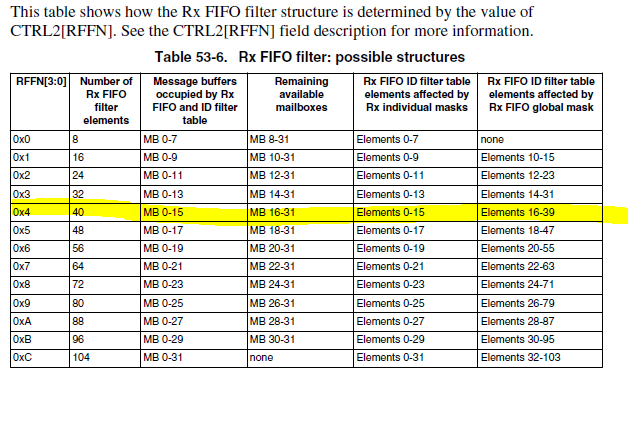

To work with your configuration because You set 40 Filters ID and I supposed as only 8 as default the problem change because occupy more MBs for filters ID. Here is a table that correlates the size of filters ID and the space used as MBs for them.

So you need to increase the MBs No from configuration because you use all of them for RxFIFO. Then the next available MBs Index will be 16, that can be used as Tx. I hope this clear your scenario.