- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Software Forums

- :

- S32 SDK

- :

- Re: How to get a clock with any frequency at FlexIO I2S module of S32K144?

How to get a clock with any frequency at FlexIO I2S module of S32K144?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to get a clock with any frequency at FlexIO I2S module of S32K144?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

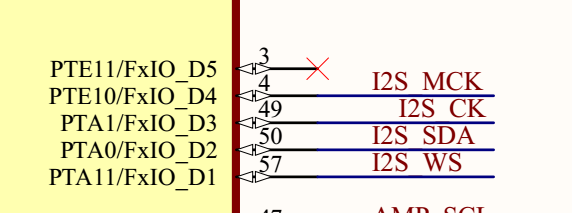

I used Flexio to simulate I2S communication,use SDK example.the SDK example offered a demo for flexio i2s,include 4 pins(SCK,WS,TX,RX),it's a three wires i2s protocol,but now we need a four wires i2s protocol(MCLK,SCK,WS,TX,no need rx),so we need to patch a master clock(MCLK,PTE10) for four wires I2S .Our flexio peripheral clock is 48MHz(or can configure it to 112MHz).we all known,audio signals often require a clock that is not an integer multiple,MCLK = (128,196,256...)* Fs, Fs may equals 22.05kHz,26.8kHz,28.2kHz,44.1kHz...).If we divide from Flexio timer,MCLK will not produce the frequency I need,because it only has integer multiples frequency.So Is there any other way to get the any frequency I need?In addition,how to ensure that the phase of MCLK we generated is the same as SCK?Looking forward to your reply。Many thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please take a look at this application note:

AN4955 Emulating the I2S Bus Master with the FlexIO Module

The example there uses MCLK.

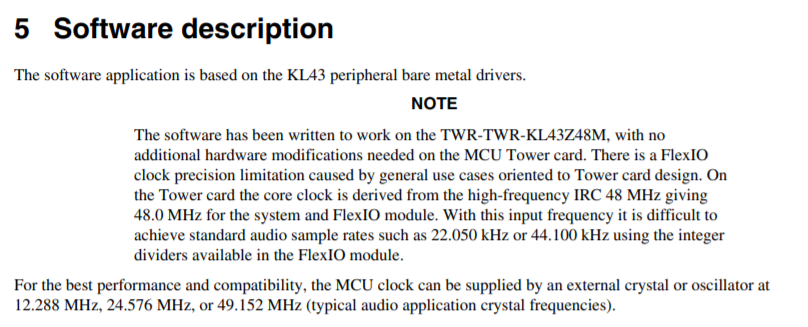

But as you mentioned, it is difficult to get the standard frequency from the 48MHz clock.

The application note recommends using special crystals.

BR, Daniel