- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- Re: I'm porting DM8806 L2switch to LS1021a IOT based board, I'd like anyone to give me an answer, hint or tip. I've some problem.

I'm porting DM8806 L2switch to LS1021a IOT based board, I'd like anyone to give me an answer, hint or tip. I've some problem.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I'm porting DM8806 L2switch to LS1021a IOT based board, I'd like anyone to give me an answer, hint or tip. I've some problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm porting DM8806 L2 switch to LS1021a IOT based board in u-boot.

Here's my porting list.

1. eTSEC1, eTSEC2 : MII

2. changed proper phy address

3. serdes is disabled

4. ncw related to SRDS_PRTCL_S1(bit 128 - 135) is set to 0x00 to prevent eTSEC->ecntrl register from being set SGMII.

and so on.

The result is

1. MDIO/MDC communication is good.

2. ethernet link is done.

3. ping Tx/Rx is not working.

u-boot serial log

=> ping 192.168.1.150

ecntrl init = 0x2d10020 : 0x1000 : 0x1000

maccfg2 init = 0x2d10504 : 0x7105 : 0x7105

priv->interface = 0x0

phy_read: addr = 0x2, devad = 0xffffffff, regnum = 0x1

phy_read: addr = 0x2, devad = 0xffffffff, regnum = 0x1

phy_read: addr = 0x2, devad = 0xffffffff, regnum = 0x4

phy_read: addr = 0x2, devad = 0xffffffff, regnum = 0x5

eTSEC1: link.

adjust_link() ecntrl = 0x2d10020 : 0x1000

Speed: 100, full duplex

Using eTSEC1 device

eTSEC1: tsec: tx error

eTSEC1: tsec: tx buffers full

ping failed; host 192.168.1.150 is not alive

=>

The debug result is

TXBD_READY(named R bit) bit is NOT cleared in Transmit data buffer descriptors (TxBD) : LS1021ARM.pdf, page1494

static int tsec_send(struct eth_device *dev, void *packet, int length)

{

......

/* Wait for buffer to be transmitted */

for (i = 0; in_be16(&txbd[tx_idx].status) & TXBD_READY; i++) { ==> not cleared

if (i >= TOUT_LOOP) {

debug("%s: tsec: tx error\n", dev->name);

return result;

}

}

tx_idx = (tx_idx + 1) % TX_BUF_CNT;

result = in_be16(&txbd[tx_idx].status) & TXBD_STATS;

return result;

}

thanks for reading. waiting some helpful answer...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Look at the Section 32.1.1.1.2.1 of the LS1021A Reference Manual for SERDES disabling.

This Section recommends setting the SRDS_PRTCL_S1 to 0xFF, the SRDS_PLL_REF_CLK_SEL_S1 to 0b00 and the SRDS_PLL_PD_S1 to 0b11 if SERDES is not used.

The LS1021A Reference Manual is available on the following page:

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried to do ping test after doing below.

1. SRDS_PLL_PD_S1 = 2'b11

2. SRDS_PLL_REF_CLK_SEL_S1 = 2'b00

3. SRDS_PRTCL_S1 = 8'hFF

but ls1021a CANNOT BE booted if SRDS_PLL_PD_S1 = 2'b11 or SRDS_PRTCL_S1 = 8'hFF.

No u-boot message is printed in serial terminal(Tera Term).

The current boot mode is SD-CARD.

Here's NCW setting

0608000a 00000000 00000000 00000000

ff000000 00c07900 60040a00 21046000

00000000 00000000 00000000 20038000

20084800 6d877340 00000000 00000000

ff000000 ==> SRDS_PRTCL_S1 = 8'hFF

00c07900 ==> SRDS_PLL_PD_S1 = 2'b11

What is the matter? Something is wrong. I think your reply is right.

Please, give me an advice, hint, tip, what is wrong.

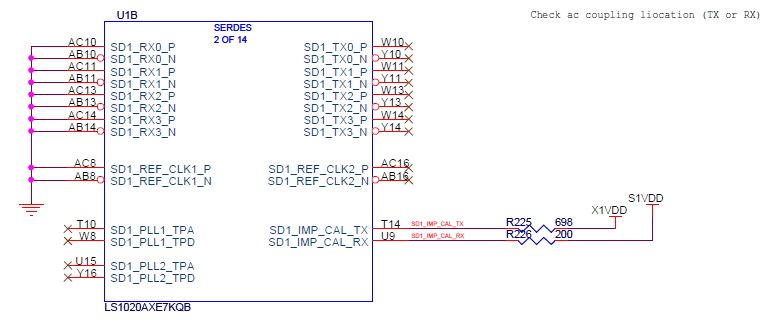

Serdes is NOT used in our HW board(based on LS1021a IOT).

Have a nice day. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for replying. It will be helpful to me.

I did this list below before your answer.

1. LS1021a and DM8806 interface is MII.

2. NCW setting of EC1(eTSEC1), EC2(eTSEC2) is MII.

3. According to L2 ethernet switch datasheet, auto-negotiation is disabled. L2 SW FORCED setting is done.

(1) Force Mode Enable.

(2) Force Link ON.

(3) Force Duplex : Full-duplex mode.

(4) Force Speed : 100M

4. temporarily setting : SRDS_PRTCL_S1(bit 128 - 135) = 0x00 to avoid setting SGMII.(will be updated soon as your answer, Section 32.1.1.1.2.1).

5. phy address is modified to refer to DM8806 datasheet.

The result is NO MORE Tx buffers full. Buffer problem is gone. but, ping still isn't working.

Serial log can be seen below.

=========================================================================

=> ping 192.168.1.61

ecntrl init = 0x2d10020 : 0x1000 : 0x1000

maccfg2 init = 0x2d10504 : 0x7105 : 0x7105

priv->interface = 0x0

phy_read: addr = 0x2, devad = 0xffffffff, regnum = 0x1

phy_read: addr = 0x2, devad = 0xffffffff, regnum = 0x1

phy_read: addr = 0x2, devad = 0xffffffff, regnum = 0x0

bmcr = 0x2100, speed = 0x64, duplex = 0x1

eTSEC1: link.

adjust_link() ecntrl = 0x2d10020 : 0x1000

Speed: 100, full duplex

Using eTSEC1 device

arp_raw_request(): eth_hdr_size, = 14, ARP_HDR_SIZE = 28

eth_send(): fffeca80, len = 42

tsec_send(): fffeca80, len : 42

status0 : 0x0

len : 42

tpkt addr = [0x2d106e4]0x1000000, data = 0x1

rpkt addr = [0x2d106a0]0x0, data = 0x0

tbyt addr = [0x2d106e0]0x40000000, data = 0x40

rbyt addr = [0x2d1069c]0x0, data = 0x0

ecntrl addr = [0x2d10020]0x8100000, ecntrl = 0x1008

maccfg1 addr = [0x2d10500]0x7000000, maccfg1 = 0x7

maccfg2 addr = [0x2d10504]0x5710000, maccfg2 = 0x7105

arp_raw_request(): eth_hdr_size, = 14, ARP_HDR_SIZE = 28

eth_send(): fffeca80, len = 42

tsec_send(): fffeca80, len : 42

status0 : 0x2000

len : 42

tpkt addr = [0x2d106e4]0x2000000, data = 0x2

rpkt addr = [0x2d106a0]0x0, data = 0x0

tbyt addr = [0x2d106e0]0x80000000, data = 0x80

rbyt addr = [0x2d1069c]0x0, data = 0x0

ecntrl addr = [0x2d10020]0x8100000, ecntrl = 0x1008

maccfg1 addr = [0x2d10500]0x7000000, maccfg1 = 0x7

maccfg2 addr = [0x2d10504]0x5710000, maccfg2 = 0x7105

ping failed; host 192.168.1.61 is not alive

=>

=========================================================================

As TPKT, TBYT register value, ping packet is seen to be SENT. but L2SW(DM8806) DID NOT receive any ping packet.

I need:

1. Example of block diagram between LS1021a and DM8806(or any other L2 SW) WITH "MII" connection.

2. Example of essential HW "MII" pin connection and configuration in ls1021a.

3. Essential "MII" configuration IN U-BOOT ls1021a.

I'll follow your answer(the Section 32.1.1.1.2.1 of the LS1021A Reference Manual for SERDES disabling), and report soon.

Thank you very much, and have a nice day.