- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

I have debugged the SPI slaver with DMA successfully. But when I found some question that I let this SPI slaver communicate with a SPI master moudle. I think some frames are lost. I think the reason is SPI slaver fill buffer to SPI Tx FIFO and recieve data from Rx FIFO if DMA controller is idle. But as a SPI slaver, once master send data with clock, slaver must recieve it and send data immediately without any pending. So if MCU is busy on memory operation, at the same time SPI master send some data, then some data frames lost. Am I right, and how to deal with the problem. Please give some code or Detailed description, thank you very much.

已解决! 转到解答。

If you see datasheet, DSPI characteristic, minimum SCK cycle time is specified as 125/83ns (for MTFE=0/1) what gives me maximum frequency of 8/12MHz.

Thank for your help.

I check the SR of DSPI, the TFUF and RFOF is not active. So I check my code and find that I start DMA transmission second time, but I havn't waited all DMA done flag for first transmission, so I add the waiting code and it seems not lost frames.

But I want to confirm which memory access priority is higher, dma controller or cpu instruction. If cpu is higher, will spi slaver lost data?

I also find a new problem, and need your help. Mcu as a Spi slaver communicate with moudle as a Spi master.

Moudle send 88 99 AA to MCU, and MCU send AA 99 88 to moudle.

When sclk=6MHz, MCU receive 88 99 AA,moudle Receive AA 99 88. It's ok.

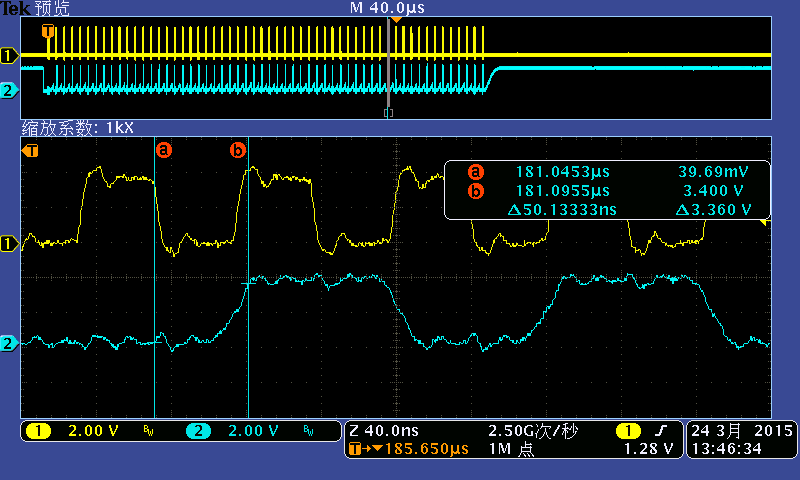

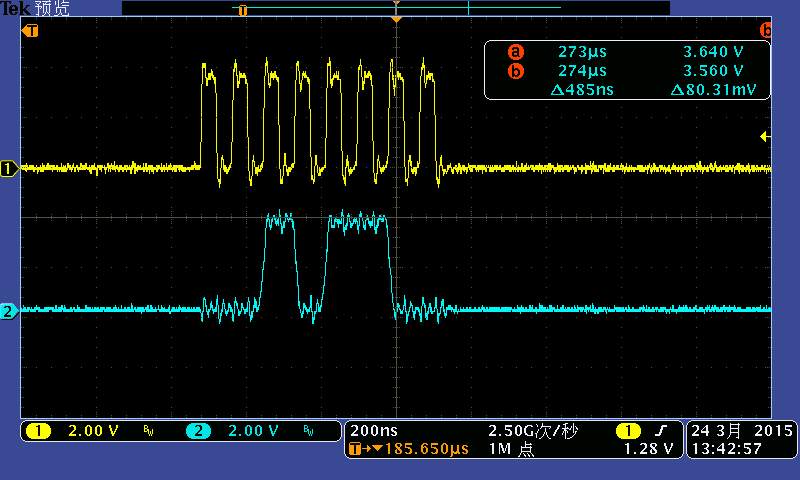

When sclk=12MHz, MCU receive 88 99 AA, but moudle recceive D5 CC C4. It seems that the highest bit is lost in high sclk. I also check the slaver Tx fifo is filled rightly(AA) before receive master's sclk.

I don't find the reason. Each SPI wire(SCLK CS MOSI MISO) length is about 10mm, MCU is MPC5605 its clock is PLL 8MHz to 64MHz. Please help me, thank you.

XBAR priority for eDMA master must be set for higher value than the core, it is basically mandatory for such applications. However this device have set fixed XBAR priorities the way eDMA has higher priority then the Core, so it is right.

According to your description I am not sure if you trigger DMA channel proper way. It is needed to use DMA source related to DSPI (DSPI_n_TX or DSPI_n_RX thus source 1-12) for proper command filling and result draining.

It is quite high frequency to drive over piece of wire. You may try to change slew rate control (SIU_PCRx[SRC]) to 1 (medium/fast).

I also send SPI frames without same, it lost bit too. Then I observe the SPI wave on oscilloscope, SPI CPHA=0(data change on SCK's down edge), but I see there is 50ns delay between sclk down edge and data change edge. So after I caculate, I think I can only use SPI slaver with lower than 10MHz sclk. I have already changed slew rate to fast. It seems a trouble.