- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

I2C specification question

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Sir / Madam,

I have a few questions, and I hope some which can help me interpret the I2C bus specification.

The I2c specification shows a SDA/SCL slope control – rising /falling time for 400KHz speed (Fast Mode) as 20nS + Cb*0.1 [ where Cb is bus capacitance] , which is shown as attachment(red square).

I would like to know:

- 1. What is the intention for this parameter? Why it's on the 400kHz bus speed requirement but not on the 100kHz?

- 2. What will be happened if tr/tf smaller than 20ns on the 400KHz bus speed requirement?

Sincerely,

Thank you,

Jerry.chien

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi David,

I have the same question for tr/tf. Is it must to meet the min time 20ns+0.1*Cb?

What happen if tr/tf is smaller than 20ns?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Jerry,

I hope all is great with you.

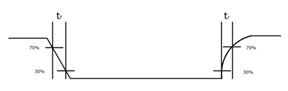

First, tr is defined as the amount of time taken by the rising edge to reach 70% amplitude from 30% amplitude for either SDA and SCL, while tf is defined as the amount of time taken by the falling edge to reach 30% amplitude from an amplitude of 70%.

Note that the rise time is defined by the external parameters: pullup resistor and capacitive load values. Fall time is determined by the output driving capabilities, pullup resistor and capacitive load values.

Usually, the I2C output specifications can be obtained from the IBIS model.

Let’s assume that this model shows that the I2C output impedance is about 40 Ohm. For maximum specified 400pf load, so the fall time is R*C ~ 20ns. This time complies with the I2C-bus specification.

The rise time is defined by the pullup resistor as below. The minimum pullup value is determined by the output capabilities of all devices on I2C bus.

R*400pF<1000ns (maximum value is specified by the I2C standard).

So, R must be less than 2.5K to support maximum load 400pF.

I hope this information helps.

Regards,

David