- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hi all,

Recently,I use the switch of SJA1110 to develop our product.Firstly,i use the S32G develop kit(S32G-VNP-RDB2) to test the switch function and it work normally.The project i used is switch_config_s32g_vnp_rdb, which is the demo project in SJA1110 SDK and the version of the SJA1110 on the develop kit is version A.Later,i download the project in our product,which version of the SJA1110 is version B.Comparing with version A,the version B SJA1110 just lack of one 100Base-T1 and other pin are same.So i modify the demo project(switch_config_s32g_vnp_rdb) configuration.I just change the version from A to B and delete the last port and phy configuration in the configuration tool and then update the code and download it into my product.After doing that,i test the DEVICE_CFG_N pin status and it turn down.That means the switch has been configured successfully.However,when i connect the wire between the SJA1110 100Base-TX port and my PC,my PC cannot recognize the wire port.

To sum up,i have two mainly question:

(1)Who can tell me if my configuration is wrong or is lacking anything?

(2)What's the software configuration different between SJA1110 version A and B?

已解决! 转到解答。

Hi @leo_liu2

If you are using MAC to MAC configuration, I assume you should check Phyless in your configuration (see screenshot attached). Also, for RGMII adding TX and RX delay to the clock signals can be necessary.

Best regards

Kevin

Hi @leo_liu2 ,

In order to help you solve your problem, I need further information. The software configuration for SJA1110A and SJA1110B is - in general - identical. Only difference is the port configuration of the xMII interfaces.

So, on the S32G development kit, port 2 of SJA1110 is connected via RGMII to an external PHY (AR8035). Please refer to the block diagram attached.

If the configuration for port 2 of the example project (switch_config_s32g_vnp_rdb) does not work on your design, my assumption would be that there are some differences between your design and the S32G development kit.

Can you provide a similar block diagram like the one I attached of port 2 of your design? From switch to PC.

- is there an external PHY connected to port 2 of the switch (Switch port 2 --> ext. PHY --> PC)?

- are you intending to use RGMII aswell? If yes, did you consider setting the delay lines? Maybe the delay line settings from the S32G example project do not fit to your design

Thank you.

Best regards

Kevin

Hi Kevin,

Thanks for your reply,the problem i mention before is solved.It's cased by some hardware design fault from our side.

Recently,i have met a new problem need to help.We use SJA1110 P2 to connect our SOC by RGMII mode(Switch port 2 --> SOC) .Our hardware designed is MAC to MAC connect between SJA1110 P2 and our SOC.After download the firmware into the switch,i use my PC to ping to the switch by SJA1110 P1(100Base TX) and it can ping successfully.That means switch is working success.However,when we check the device detect by our SOC,it can not found the eth interface.That means SJA1110 P2 can not be recognize by our SOC.The hardware design and software configuration is shown as the block diagram attached.Can you help me to solve this problem.

Thank you.

Best regards

Hi @leo_liu2

If you are using MAC to MAC configuration, I assume you should check Phyless in your configuration (see screenshot attached). Also, for RGMII adding TX and RX delay to the clock signals can be necessary.

Best regards

Kevin

Hi Kevin,

Follow your advise,i check the checkbox of Phyless in my configuration and download it into the SJA1110.When i test the function of SJA1110,i found that SJA1110 seems does not work,because when i try to ping the SJA1110 through the 100Base TX(P1),it can not ping success.Is there any configuration i have forgot?

Can you show me the complete configuration step of the siwtch for the scene of using the SJA1110 P2 and P3 connnet to the SOC by MAC TO MAC.

Beside ,i am confuse the method you menthion " for RGMII adding TX and RX delay to the clock signals can be necessary" ,is that means change the "TXC Delay Phase" and "RXC Delay Phase" in MII3 -Internal Delay Tab?

Best regards

Leo

Hi @leo_liu2

There is actually a suitable example in the SJA1110 SDK available. You can import it by performing a right click in the project explorer -> New -> SDK Project from example -> then search for sja1110 and import the "switch_config_sja1110evm" project.

In the switch configuration, Port 2 of switch 1 is configured as RGMII and supposed to be connected to an SoC via the SABRE interface.

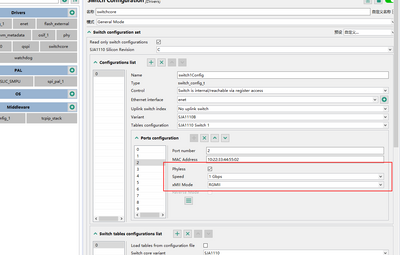

Regarding RX and TX delay: the switch can add those to both RX and TX clock (in case the corresponding link partner does not do so). It can be configured for MII2 and MII3 in the pins configuration of the SJA1110 (see attached screenshot). In the example from the screenshot both delay lines are activated. Please note that these settings can be different on your end.

I hope this does help.

Best regards

Kevin

Hi Kevin @kaden ,

I have configured the switch P2 to the way you mention,however,our SOC still can not detect the ethernet port.The attachments blocks is the configuration i set.

Can you help me to check whether the configuration i set is corrected or not?

Besides,are there anyway to help me know whether the switch P2 is configured successfully and work,we can not recognize whether the problems is caused by switch port or caused by SOC.

Best regards,

Leo!

Hi @leo_liu2 ,

what are the TX and RX delay settings? Does the SoC add either TX or RX or both delays or not? If not, the switch needs to be configured to add these delays. If the SoC does add them, the switch should not add any delay.

BR

Kevin

Best Regards.

Hi ,This is the MAC Port that connect directly to the SOC in our design.With the congifuration show in the figure,the MAC work normally , SJA1110 and SOC can PING each other successfully.Hope this can help you .

Best Regard.

I have the same switch MAC Port configuration with you, but still ping failure between SJA1110 and SOC, you said your problem is caused by soc sides, Can you provide some details? and share the soc configuraton to me?

Best Regards.

Hi @leo_liu2 ,

we are sorry but please expect some delay here caused by Christmas vacations. My expectation is that this will be answered in first week in January. Hope it is ok.

Regards,

Lukas