- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- Other NXP Products

- :

- Re: FS26 SBC init delay

FS26 SBC init delay

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

I have a question regarding the FS26 SBC.

Is more delay needed in the following situations?

Standby -> SPI wake up -> delay 1.5ms -> SBC init

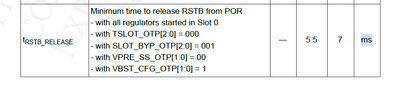

For 1.5ms, I referred to the phrase below in the datasheet.

SPI chip select wake-up:

– When the SPI wake up is enabled, the device wakes up with any activity on the SPI bus (transition from high to low of CSB pin).

– In case of a SPI wake up, the first SPI command is ignored, and the FS26 will be ableto respond to the subsequent SPI commands after 1.5 ms.

However, init fails with 1.5ms.

Init succeeds with 10ms.

Is there an exact delay guide?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No fully understand you wrote:

init fails with 1.5ms.

Init succeeds with 10ms.

Could you please give more explain?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes.

Standby -> SPI wake up -> delay 1.5ms -> Sbc_fs26_Init

-> return Not Ok

Standby -> SPI wake up -> delay 10ms -> Sbc_fs26_Init

-> return Ok

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Set this time above 7ms.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SBC Standby -> SPI wake up -> delay 1.5ms -> Sbc_fs26_Init

-> return Not Ok

SBC Standby -> SPI wake up -> delay 10ms -> Sbc_fs26_Init

-> return Ok

I don't know why you are talking about RSTB time.

If I put the SBC in Standby, the SBC will not become a POR.

When MCU do SBC SPI wakeup, RSTB has already been released.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

---

I don't know why you are talking about RSTB time.

If I put the SBC in Standby, the SBC will not become a POR.

When MCU do SBC SPI wakeup, RSTB has already been released.

---

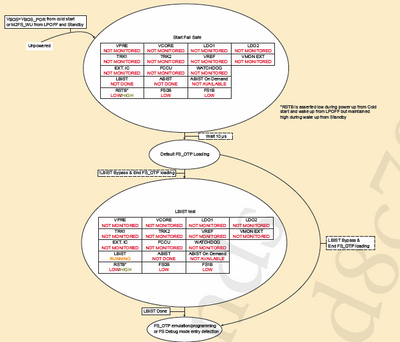

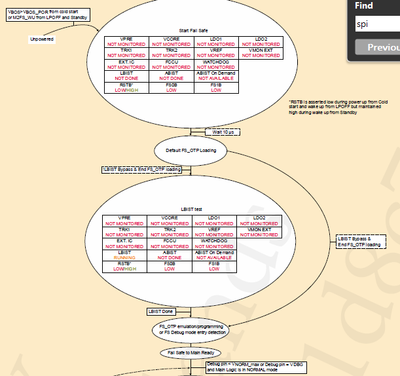

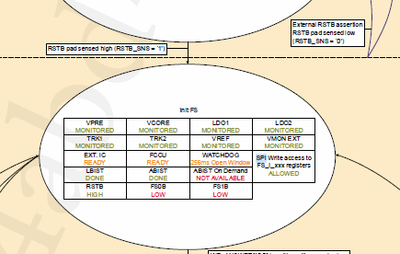

After wake up SBC state machine still follow below, detail in datasheet page25:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes.

It says "but maintained high during wake up from Standby" on it.

so

SBC Standby (RSTB High) -> SPI wake up (RSTB High)-> delay 1.5ms (RSTB high) -> Sbc_fs26_Init(RSTB high) -> return Not Ok

RSTB is always high, so why is RSTB Release time and delay related?

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Although RSTB is high but the state machine still follow:

Default FS_OTP Loading->LBIST DONE->ENABLE Monitoring->ABIST1 test->enter INIT FS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Very Thank you I understood

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think below process:

Standby -> SPI wake up -> delay 1.5ms at same time the fail safety mechanism continue to flow as below picture if no failure will stop in INIT phase -> SBC init