- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- RFID / NFC

- :

- NFC

- :

- NTAG NT3H2111 Pass Through Mode doesn't work

NTAG NT3H2111 Pass Through Mode doesn't work

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

NTAG NT3H2111 Pass Through Mode doesn't work

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I am trying to use the NTAG NT3H2111 2K pass through mode with no success at all. First I programmed and checked the following: read session register, write session register, read memory (16 bytes), write memory (16 bytes).

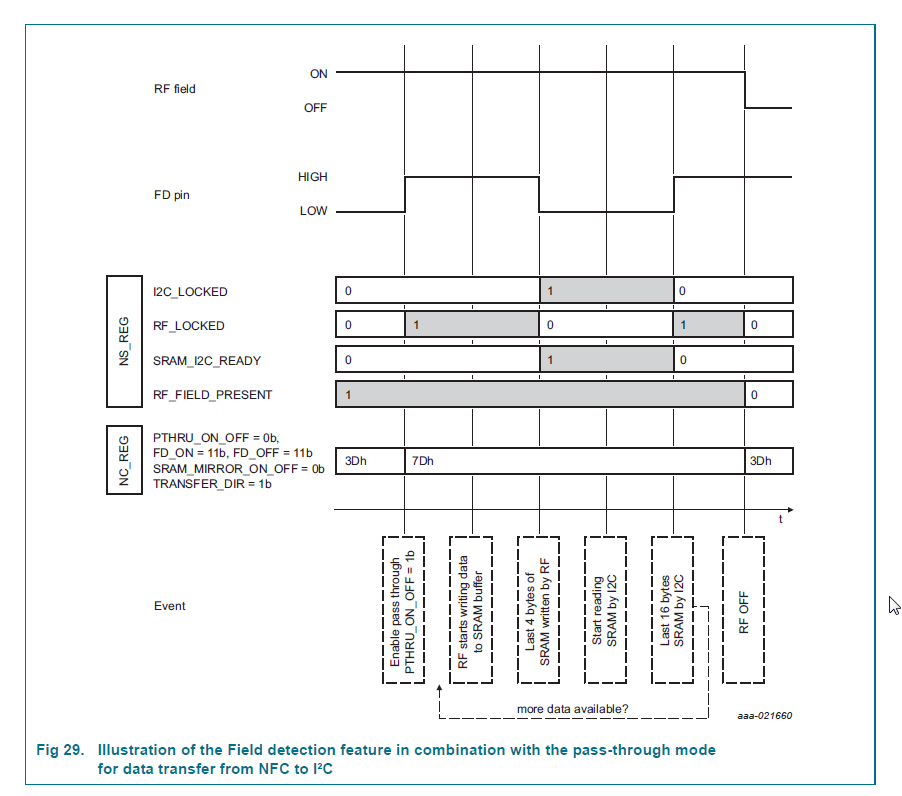

Following a presentation of pass through mode and the instructions on the datasheet I tried implementing pass through mode as follows:

1) On session register NC_REG (00h): set PTHRU_ON_OFF=1b (#6 bit), set TRANSFER_DIR=0b( From I2C to NFC, #0 bit) - this step can be done on "1 shot"

2) Wrtie 64 byets to the SRAM - 16 bytes at a time for 4 cycles (Loop)

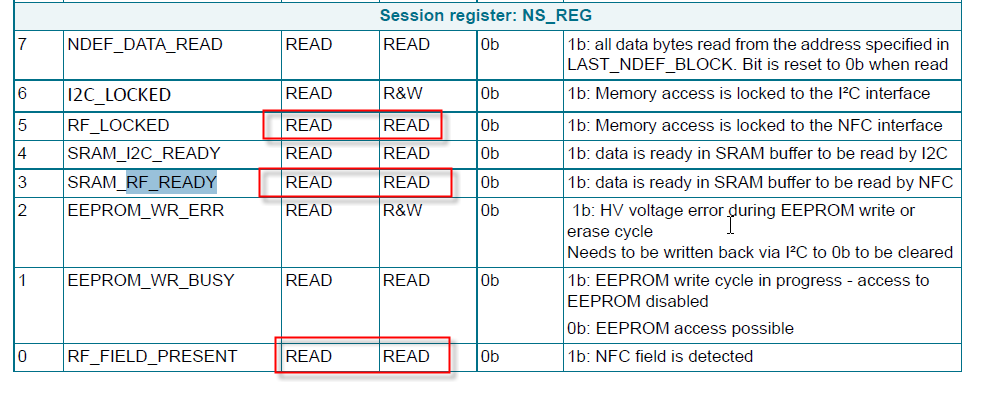

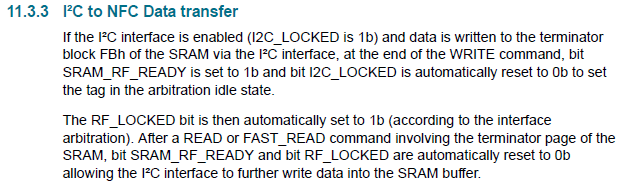

3) Set NS_REG (06h) bit SRAM_RF_READY (#3 bit) to be 1b. I2C_LOCKED (#6 bit) is automatically reset to 0b to set the tag in the arbitration idle state. The RF_LOCKED (#5 bit) bit is then automatically set to 1b

4) Do polling on NS_REG (06h) bit SRAM_RF_READY (#3 bit) - wait for it to be 0b

5) Write to the SRAM again

I'm not sure if this is the right way to do it. Is there anything else I'm missing?

Thanks,

Matan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Matan,

As the data sheet says"The pass-through mode can only be enabled via I2C interface when both interfaces are

powered." so have you checked if the RF field is already available at the beginning of the pass-thru mode?

Please kindly refer to the following for more details.

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kan Li,

Thank you for your answer.

What I described in the implementation is I2C -> NFC direction (you referred to NFC ->I2C direction). Anyhow, NS_REG bit RF_FIELD_PRESENT works well and recognize the mobile phone.

Since I don't use FD pin it's irrelevant for the sequence I described. Is my sequence correct?

Will it be easier to use FD pin instead of polling NS_REG?

On the datasheet it says that " Set NS_REG (06h) bit SRAM_RF_READY (#3 bit) to be 1b. I2C_LOCKED (#6 bit) is automatically reset to 0b to set the tag in the arbitration idle state. The RF_LOCKED (#5 bit) bit is then automatically set to 1b" But I think none of the automatic bit changes occur.

Can you please advise?

Thanks again,

Matan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Matan,

It depends on how you implement your application, if you prefer interrupt driven mode, FD detect is better.

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kan Li,

I've done some more debugging on my sequence and I think I know where is the problem: After writing to the SRAM - NS_REG is set to 41h (I2C_LOCKED = 1b and RF_FIELD_PRESENT= 1b)

According to the description on the datasheets, I need to set SR_RF_READY to 1b and then automatically I2C_LOCKED needs to turn to 0b.

I want to confirm the MASKING and REGDAT stages for this change:

NS_REG prior to the change: 41h, after change: 21h

option 1: If SR_RF_READY bit sets all the other bits automatically than

MASKING: 08h

REGDAT: 49h

option 2: if SR_RF_READY bit does not sets all the other bits automatically than

MASKING: 68h

REGDAT: 29h

An example for something I have already done and works:

to turn ON pass through mode: I changed NC_REG from 01h to 40h by MASKING: 41h , REGDAT: 40h.

can you please advise?

Update: I tired to force NS_REG to be 29h: meaning RF_LOCKED bit = 1b ,SRAM_RF_READY = 1b, RF_FIELD_PRESENT = 1b (since the mobile phone is connected - on top of the antenna) -> after writing to the SRAM, but NS_REG value did not changed at all

Many thanks,

Matan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Matan,

I am sorry, but in my understanding, RF_LOCKED bit ,SRAM_RF_READY and RF_FIELD_PRESENT are status bits, force writing may not take effect, and only the tag may change them in some condition. Please refer to the following for details.

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kan Li,

Thank you very much for clarifying.

I would like you to help me understand what triggers the bit change under this sequence:

is bit SRAM_RF_READY being triggered by finishing WRITE command? or: by finish writing to FBh of the SRAM?

currently I can switch ON pass through mode and conduct the writing, but I want to trigger NS_REG so the mobile App will collect the data.

Thanks,

Matan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Matan,

I think it should be by finish writing to the terminator block FBh of the SRAM.

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------