- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Model-Based Design Toolbox (MBDT)

- :

- Model-Based Design Toolbox (MBDT)

- :

- Re: S32K3 MBDT - SPI clock poor timing

S32K3 MBDT - SPI clock poor timing

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K3 MBDT - SPI clock poor timing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have encountered two issues relating to the SPI clock on a S32K344 when integrating with an ADE7912.

- There is an undesired leading pulse on the SPI clock causing a bit-shift, corrupting the data.

- I am unable to resolve this issue by delaying the chip select, as the chip select is on a MUX IC and controlled through GPIO. I have attached my SPI configuration from the S32 configuration tool, and the output from a logic analyzer.

- The clock duty cycle is not fixed at 50% when at high speeds. At 4MHz, the duty cycle of the clock is around 65% which does not meet the timing requirements of the selected SPI device. Lowering the SPI clock speed to 2MHz results in a duty cycle of 58%. Please advise how to ensure a 50% duty cycle at 4MHz.

Any advise for resolving these issues would be appreciated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

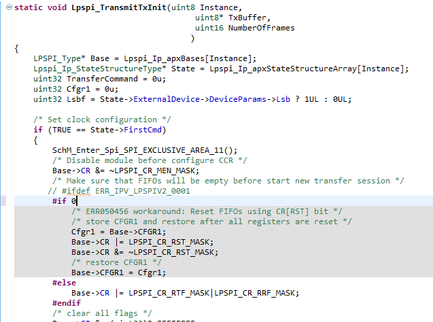

1) seems the behavior you see is due to driver implementation of a workaround for errata 0050456, when module reset is used. This puts clock pulse and sets SOUT high until data is transmitted. This is not an issue for slave devices if really controlled by CS and SCK, but for usage you have it would bring issue.

Try to do not use module reset and keep resetting the FIFO using CR[RTF] and CR[RRF]

2) this can be issue of the analyzer sample rate, but also for higher rates, try to increase pins drive strength.

3) to read more bytes from slave you need to send required dummy bytes from master keeping CS selected.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your response @PetrS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In addition to the issues described above, I have been unable to find a way to have the SPI clock continue after the MOSI signal is complete. During a read operation, the slave device requires a clock signal to continue pulsing while the response is broadcasted on MISO. Can you provide instructions on how to configure SPI for a read operation.