- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Receiving garbage value in Rqueue?

Hi,

I am using EQADC_A and EQADC_B.

I am using CFIFO_1 for transmitting 10 commands from Cqueue to CFIFO through DMA.

I am receiving ADC0 data in RFIFO_1 and ADC1 data in RFIFO_2 and sending this data to Rqueue_1 from RFIFO_1 and Rqueue_2 from RFIFO_2.

So for EQADC_A i am getting the correct result in Rqueue_A_1 from RFIFO_1 and Rqueue_A_2 from RFIFO_2.

But for EQADC_B i am getting correct result in Rqueue_B_1 from RFIFO_1 but getting garbage in Rqueue_B_2 which is out of range and also the count is not varying when i vary the voltage range.

As i also checked the result in RFIFO 2 for EQADC_B by reading EQADC_B.RF2R[n].B.RFIFO2_DATAW register so i get the correct output but when this data is stored in Rqueue_B_2 then data not coming properly some garbage value are displayed.

i also checked the DMA configuration for both EQADC A and B which correct.

Can you suggest me the solution?

Why this is happening?

Hi, could you share your configuration?

Any progress?

If not you could show me DMA configuration for Rqueue_B_2 or the whole project.

I have no idea until now.

DMA configuration:-

void eDMA_B_init(void)

{

// eDMA Control Reg: set round robin arbitration, ERGA=1,ERCA=1,EDBG=0

DMA_B.CR.R = 0x0000000C;

// eDMA Enable Error Interrupt Register Channels 63:32

DMA_B.EEIH.R = 0x00;

// eDMA Enable Error Interrupt Register Channels 31:00

DMA_B.EEIL.R = 0x00;

// eDMA Enable Request Register Channels 63:32

DMA_B.ERQH.R = 0x00;

// eDMA Enable Request Register Channels 31:00

DMA_B.ERQL.R = 0x00;

}

Command send from Cqueue_B_1 to CFIFO 1:-

void eqadc_B_sendcommand(void)

{

// initialize TCDs

eDMA_TCD_eQADCB_CFIFO_init(2, &CQueue_B_1, (void *)&EQADC_B.CFPR[1], sizeof(CQueue_B_1)/4);

eDMA_TCD_eQADCB_RFIFO_init(3,(void *)&EQADC_B.RFPR[1], &RQueue_B_1, sizeof(RQueue_B_1)/2);

eDMA_TCD_eQADCB_RFIFO_init(5,(void *)&EQADC_B.RFPR[2], &RQueue_B_2, sizeof(RQueue_B_2)/2);

}

void eDMA_TCD_eQADCB_CFIFO_init(vuint8_t DMA_chan, void *cmd_source, void *cmd_dest, vuint32_t cmd_count):- declaration of function

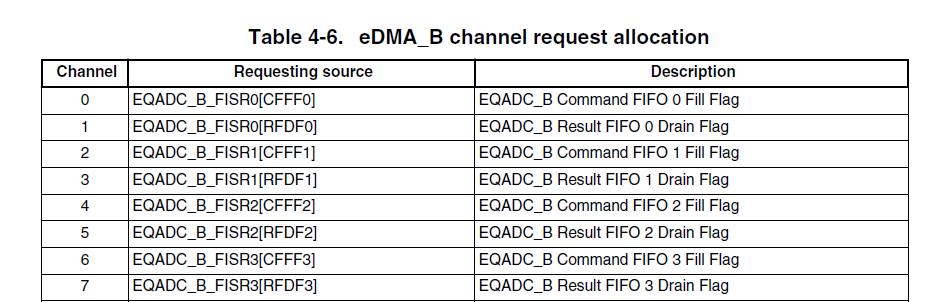

here 2,3 and 5 are DMA channel number according to this snap

This is too little information. Please provide all eQADC and eDMA setup. Actually which device you are using?

Have you checked example code for eQADC I have shared here?:

Hi David

We are using S32 Design Studio.

S32 Design Studio for Power Architecture

Version: 1.2

Build id: 170613

(c) Copyright Freescale Semiconductor 2016. All rights reserved.

(c) Copyright NXP 2017.

MCU == MPC5777C

evb == MPC5777C EVB debugger == Multilink universal fx

Operating System == Win7x64,Win8x64

EQADC initialization:-

void eqadc_A_init(void)

{

EQADC_A.MCR.R = 0x00000000; // Synchronous Serial Interface-Disable; Debug-Disable

EQADC_A.CFPR[0].R = 0x00800301; //Send CFIFO 0 a ADC0 configuration command

EQADC_A.CFPR[0].R = 0x82800301; //Send CFIFO 0 a ADC1 configuration command

EQADC_A.CFCR0.R = 0x04100000;

while (EQADC_A.FISR[0].B.EOQFX == 0); /* Wait for End Of Queue flag */

EQADC_A.FISR[0].R = End_of_Queue_Flag;

}

eDMA initialization:-

void eDMA_init(void)

{

// eDMA Control Reg: set round robin arbitration, ERGA=1,ERCA=1,EDBG=0

DMA_A.CR.R = 0x0000000C;

// eDMA Enable Error Interrupt Register Channels 63:32

DMA_A.EEIH.R = 0x00;

// eDMA Enable Error Interrupt Register Channels 31:00

DMA_A.EEIL.R = 0x00;

// eDMA Enable Request Register Channels 63:32

DMA_A.ERQH.R = 0x00;

// eDMA Enable Request Register Channels 31:00

DMA_A.ERQL.R = 0x00;

}

Same initialization done for EQADC_B and eDMA_B.

I am using CFIFO_1 for transmitting 10 commands from Cqueue to CFIFO through DMA for both EQADC_A and EQADC_B.

like this:-

( CHANNEL(ANA34_TO_IGBT1_Thermistor1) | B0 | CAL | MESSAGE_TAG(RFIFO1) | LST(0) ),

( CHANNEL(ANA35_TO_IGBT2_Thermistor2) | B1 | CAL | MESSAGE_TAG(RFIFO2) | LST(0) ),

( CHANNEL(ANA36_TO_IGBT3_Thermistor3) | B0 | CAL | MESSAGE_TAG(RFIFO1) | LST(0) ),

( CHANNEL(ANA37_TO_IGBT4_Thermistor4) | B1 | CAL | MESSAGE_TAG(RFIFO2) | LST(0) ),

( CHANNEL(ANA06_TO_DC_BUS_Volt_Sense) | B0 | CAL | MESSAGE_TAG(RFIFO1) | LST(0) ),

( CHANNEL(ANA07_TO_DC_BUS_Current_Sense)| B1 | CAL | MESSAGE_TAG(RFIFO2) | LST(0) ),

( CHANNEL(ANA12_TO_IoutA_Sense) | B0 | CAL | MESSAGE_TAG(RFIFO1) | LST(0) ),

( CHANNEL(ANA13_TO_IoutB_Sense) | B1 | CAL | MESSAGE_TAG(RFIFO2) | LST(0) ),

( CHANNEL(ANA14_TO_IoutC_Sense) | B0 | CAL | MESSAGE_TAG(RFIFO1) | LST(0) ),

( CHANNEL(ANA15_TO_IoutD_Sense) | B1 | CAL | MESSAGE_TAG(RFIFO2) | LST(0) | EOQ ),

I am receiving ADC0 data in RFIFO_1 and ADC1 data in RFIFO_2 and sending this data to Rqueue_1 from RFIFO_1 and Rqueue_2 from RFIFO_2.

So for EQADC_A i am getting the correct result in Rqueue_A_1 from RFIFO_1 and Rqueue_A_2 from RFIFO_2.

But for EQADC_B i am getting correct result in Rqueue_B_1 from RFIFO_1 but getting garbage in Rqueue_B_2 which is out of range and also the count is not varying when i vary the voltage range.

Hi, I don't see any initialization of eQADC_B module. Just to note there are 2 eQADC modules on this device, both consists of 2 ADC units, thus 4 converters in total.

Hi David,

Same configuration for initialization for eqadc and eDMA is done for EQADC B. there are four converter in total.

Please, show me you eQADC_B module initialization. Thanks

Hi David,

void eqadc_B_init(void)

{

EQADC_B.MCR.R = 0x00000000; // Synchronous Serial Interface-Disable; Debug-Disable

EQADC_B.CFPR[0].R = 0x00800301; //Send CFIFO 0 a ADC0 configuration command

EQADC_B.CFPR[0].R = 0x82800301; //Send CFIFO 0 a ADC1 configuration command

//EQADC_B.CFCR0.R = 0x0C101C10;

EQADC_B.CFCR0.R = 0x04100000;

while (EQADC_B.FISR[0].B.EOQFX == 0); /* Wait for End Of Queue flag */

EQADC_B.FISR[0].R = End_of_Queue_Flag;

EQADC_B.IDCR0.R = 0x33033303;

EQADC_B.IDCR1.R = 0x33030000;

}

Here is my EQADC_B initialization.