- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

MPC5746C ADC Watchdog Threshold

I am having a hard time understanding the Reference manual in regards to the ADC Threshold.

Whatever I have here is working. Now, I am trying to understand it.

First,

I set the threshold in the threshold registers.

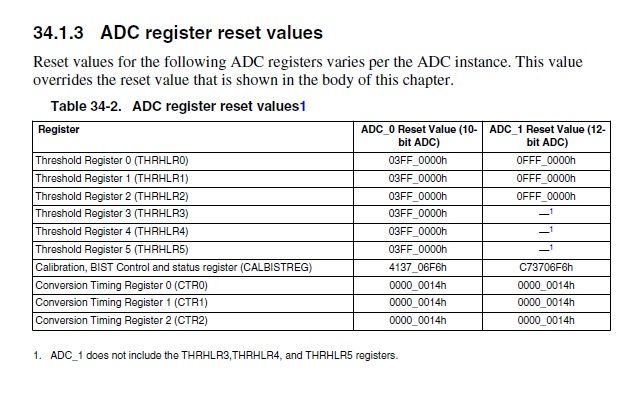

There is only 4 Threshold registers if I am not mistaken? (THRHLR0, THRHLR1, THRHLR2, THRHLR3)

ADC_1.THRHLR0.B.THRH=800;

ADC_1.THRHLR0.B.THRH=200;

Now, I select the threshold register into the ADC channel I am using

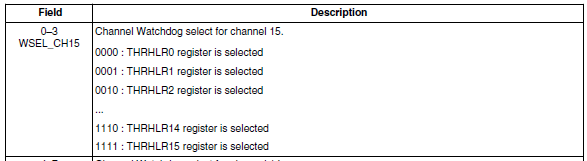

ADC_1.CWSELR1.B.WSEL_CH9 = 0x0; //0000 : THRHLR0 register is selected

The Manual mentions that I can select one of 15 threshold registers, but there seems to only be 4?

...

1110 : THRHLR14 register is selected

1111 : THRHLR15 register is selected

Now, I enable the Watchdog for Channel 9

ADC_1.CWENR0.B.CWEN9 = 1;

Here I enable the 'Watchdog Threshold Interrupt'

The problem is that there seems to be 5 watchdogs.

How did, or does, the channel specify which watchdog to use?

Is the watchdog a Threshold Watchdog and there are 4 of them?

ADC_1.WTIMR.B.MSKWDG0H = 1;

ADC_1.WTIMR.B.MSKWDG0L = 1;

Thanks,

I seem to be making some headway. It's just very cornfusing.

The Reference manual states that there are 5 threshold registers for ADC_0 and 3 threshold registers for ADC_1.

The header file MPC5746C.h rev 4.0.0 only provides for 4 threshold registers

#define ADC_0_THRHLR0 ADC_0.THRHLR0.R /* Threshold Register */

#define ADC_0_THRHLR1 ADC_0.THRHLR1.R /* Threshold Register */

#define ADC_0_THRHLR2 ADC_0.THRHLR2.R /* Threshold Register */

#define ADC_0_THRHLR3 ADC_0.THRHLR3.R /* Threshold Register */

In the fine print in the figure above, it states "1. ADC_1 does not include the THRHLR3,THRHLR4, and THRHLR5 registers."

So, I believe that ADC_1 only has 3 Watchdog registers. (0,1,2). That seems to check out.

I believe that also holds true for ADC_0, since MPC5746C.h only provides access to 3 threshold registers.

So, I am assuming that the threshold registers are the "watchdog threshold registers" and the numbers are the same. i.e. (Threshold Register 0 is equal to Watchog 0)

The following code snippet works for Threshold Register 1 / WTIMR Register 1

ADC_1.THRHLR1.B.THRH=800; // UPPER THRESHOLD

ADC_1.THRHLR1.B.THRL=200; // LOWER THRESHOLD

ADC_1.CWSELR1.B.WSEL_CH9 = 0x1; //0000 : THRHLR0 register is selected

ADC_1.CWENR0.B.CWEN9 = 1;

ADC_1.WTIMR.B.MSKWDG1H = 1;

ADC_1.WTIMR.B.MSKWDG1L = 1;

This is the CWSEL (Channel Watchdog Select Register) that states a channel could use THRHLR0 through THRHLR15

Regards,

Hi Christopher,

Your understanding is quite close to real implementation.

For each Analog watchdog there is one Threshold value (Low and High) Register (THRHLR).

There are 6 Analog watchdogs (0, 1, 2, 3, 4, 5) for ADC_0 and 3 Analog Watchdogs (0, 1, 2) for ADC_1.

So Table 34-2 is correct, showing number of implemented Threshold registers for each ADC.

The CWSEL (Channel Watchdog Select Register) should be programmed to select one of implemented analog watchdog (its Threshold register), so possible values are 0-5 for ADC_0 module and 0-2 for ADC_1 module.

WTIMR[MSKWDGxL] and WTIMR[MSKWDGxH] mask bits specify, if an interrupt is generated upon threshold violation.

As 3 watchdogs are only available on ADC_1, just lower 6 bits are accessible on ADC_1.WTIMR.

Regarding the header file; all 6 Threshold registers should be defined. You pointed to 4, another 2 are located after channel data registers. Again on ADC_1 only THRHLR0, THRHLR1 and THRHLR2 registers are accessible.

BR, Petr