- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Well, this is kind of weakness of the documentation. Sometimes names of internal signals soaked to the reference manual and it's nor clearly explained.

In this case, p_dmem_rstcfg are hardcoded signals. The result is that reset value of DMEMCTL0 register is 0x0000041B.

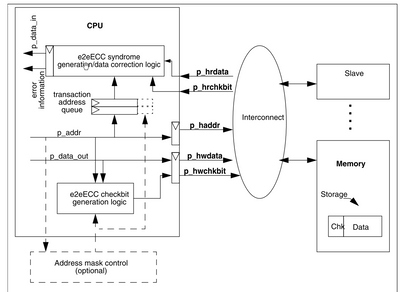

p_hwchkbit[7:0] is then internal bus for e2eECC:

Maybe this draft of application note and examples from my colleague could help:

Regards,

Lukas

Hi Jamber,

these are internal input signals of the core which are used to provide configuration information for operation out of reset. In this case, these signals are 0b0000. As defined in the RM, reset value is:

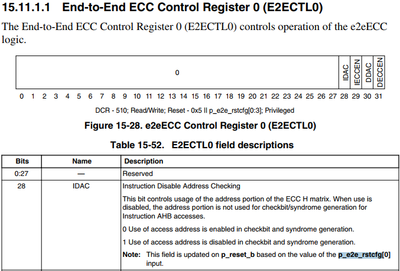

Reset - 0x5 || p_e2e_rstcfg[0:3];

That means the reset value is 0x5.

Regards,

Lukas

Well, this is kind of weakness of the documentation. Sometimes names of internal signals soaked to the reference manual and it's nor clearly explained.

In this case, p_dmem_rstcfg are hardcoded signals. The result is that reset value of DMEMCTL0 register is 0x0000041B.

p_hwchkbit[7:0] is then internal bus for e2eECC:

Maybe this draft of application note and examples from my colleague could help:

Regards,

Lukas