- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- MCUXpresso软件和工具

- :

- MCUXpresso SDK

- :

- Re: bootloader question on MAPS-K64 board

bootloader question on MAPS-K64 board

bootloader question on MAPS-K64 board

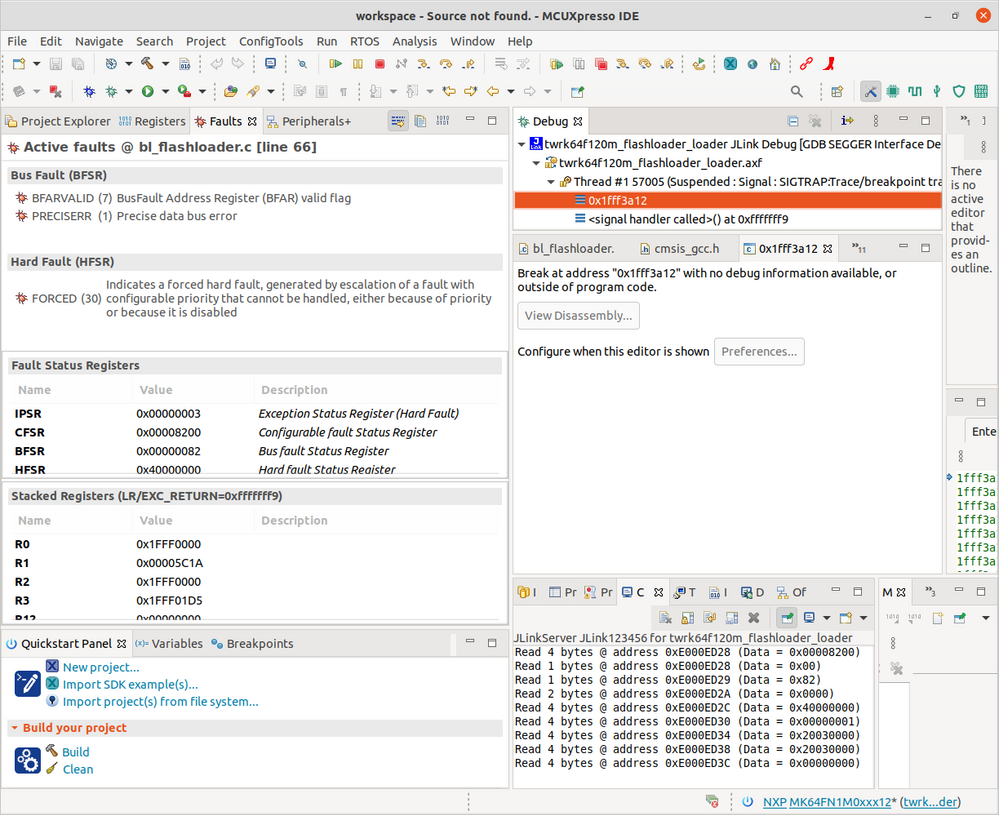

Based on towerk64f120m sdk flashloader_loader example, I run a dac_adc example on my MAPS-k64 board. The dac_adc example can run ok in the flash(at 0x0), and I build it to low ram(at 0x1fff0000) and generate flashload_image.c. When I try to use flashloader_loader example to sum it at ram, I got the problem, Attached picture is the debug screen.

MCUXpresso: MCUXpresso IDE v11.4.0 [Build 6224] [2021-07-15]

Hi @zhongshen ,

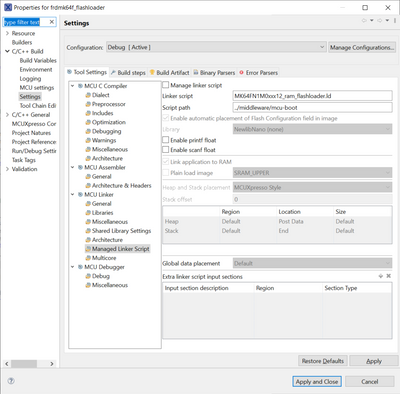

Yes, instead of the flashloader, you can let flashloader_loader put other image into SRAM and run. Do you use the same linker file from flashloader project?

You can trace flashloader_loader project to see if it copy the image correctly and get the right PC and SP address.

Regards,

Jing

sometimes run on external ram, always reset!

the attached is the source code, which can be run at internal ram. the flashloader_image.c is generated at external ram(at 0x80000000).

The debug console port is uart0, PTA1 as RX, PTA2 as TX. The loader initiate flexbus.

Hope anyone can give me advise me to solve this problem.

Hi Jing,

Thank you for you help.

So far, the problem is not solved. Here is the result:

The dac_adc sdk demo can be loaded by flashloader_loader to load in ram on chip and successfully run in it. But build dac_adc sdk demo with external ram(at 0x80000000), and then using flashloader_loader to load it at 0x80000000, setting the SCB->VTOR=0x80000000, main stack pointer and process stack pointer, after then to jmp dac_adc demo entry, I got the hard fault. I can not understand that the demo can run at internal ram, but fault to run at external ram in which all settings are same(only different address). How to solve this hard fault?

I used mcuxpresso ide to build a new project, and copy bootloader_run and bootloader_cleanup functions from flashloader_loader project. And then I can use it to run dac_adc sdk demo(link to lower ram) at ram.

I have another problem: as the maps-k64 board have 2MB sram, and I reconfigured it (flexbus) at 0x80000000, link to run dac_adc demo at lower ram(0x1fff0000), I hope to run it at 0x80000000, but the chip will reset when to jmp to 0x80000000 entry. Is it impossible to run program at off-chip sram?