- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso SDK

- :

- Re: Bug Report - LPC55S36 SDK 2.10.2 DMIC PLL1

Bug Report - LPC55S36 SDK 2.10.2 DMIC PLL1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Bug Report - LPC55S36 SDK 2.10.2 DMIC PLL1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Greetings,

I was having trouble with initializing DMIC clock from PLL1 and had to debug the SDK code.

I found a typo in the file fsl_clock.h from the SDK_2.x_LPC5536 version 2.10.2 which seems to be the source of the problem.

In the enum clock_div_name_t : the value kPLL1_to_DMIC line 941 is assigned the value 2, where the Reference Manual LPC553xRM specifies page 304 that it should be assigned value 0b100 (4).

RefMan:

011b - FRO_HF 100b - PLL1 clock 101b - MCLK in

//fsl_clock.h:940 kFRO_HF_to_DMIC = MUX_A(CM_DMICFCLKSEL, 3), /*!< Attach FRO_HF to DMIC. */ kPLL1_to_DMIC = MUX_A(CM_DMICFCLKSEL, 2), /*!< Attach PLL1 to DMIC. */ kMCLK_IN_to_DMIC = MUX_A(CM_DMICFCLKSEL, 5), /*!< Attach MCLK_IN to DMIC. */

The solution is simply to replace line 941 with the following :

kPLL1_to_DMIC = MUX_A(CM_DMICFCLKSEL, 4), /*!< Attach PLL1 to DMIC. */

The problem I had isn’t fully solved yet, still investigating, but at least now the PDM clock output is correct.

Hope it can help someone else until the next SDK update.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Could you tell me what kind of example you are based on or are you trying to run?.

Best regards,

Pavel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was using the SDK driver examples dmic_dma and dmic_i2s_dma as base, which are using kEXT_CLK_to_DMIC and kPLL0_to_DMIC respectively, so the problem mentioned in the previous message didn't occur. I just wanted to use PLL1 as clock source for the DMIC peripheral. It works well now for 1 microphone.

Now I'm trying to use 2 PDM microphones at the same time, and I'm having difficulties to understand exactly how the peripheral is supposed to manage stereo PDM :

I found some inconsistencies between the LPC553x Datasheet and the LPC553xRM concerning the naming of DMIC related pins :

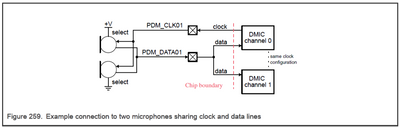

- RM mentions PDM_CLK01 (and PDM_CLK02 ?) on Figures 257 to 259, as well as in the note at the beginning of chapter 45.1.3,

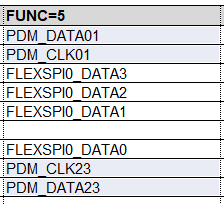

but everywhere else only mentions PDM_CLK0 and PDM_CLK1, as well as the Datasheet which only mentions those last two - RM mentions a few times in IOCON chapter its embedded Pinout Spreadsheet, in which pins are called PDM_CLK01, PDM_DATA01, PDM_CLK23, and PDM_DATA23.

- if we assume the pins PDM_*01 correspond to pins PDM_*0 and pins PDM_*23 correspond to pins PDM_*1 : there is a bigger inconsistency concerning pin PIO0_7's FUNC5 between the Pinout Spreadsheet which marks it as PDM_CLK23, whereas Datasheet marks it as PDM_CLK0

There is also ambiguity on the possibility of muxing two PDM streams on both edges through a single PDM_DATA input pin which according to RM's Figure 259 seems to be possible,

but with the issue stated above as well as the fact that the PDM_DATAn pins can seemingly only be connected to one DMIC channel, I'm not sure about this.

Would it be possible to get some clarifications for those pin routing and functionality ambiguity ?

Thanks forward,

Best regards,

OE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

if we assume the pins PDM_*01 correspond to pins PDM_*0 and pins PDM_*23 correspond to pins PDM_*1 : there is a bigger inconsistency concerning pin PIO0_7's FUNC5 between the Pinout Spreadsheet which marks it as PDM_CLK23, whereas Datasheet marks it as PDM_CLK0

I'm using LPC5536-EVK board and also just noticed that concerning the above quoted part :

on the EvalBoard the pin P0_7 is connected to the net P0_7-PDM_CLK0_ISP1 which I use as PDM clock source, and the clock output is actually enabled only when the channel 1 is enabled via the bit EN_CH1 in DMIC's CHANEN register,

which proves that the Datasheet (in Rev. 1.0) is misleading concerning pin P0_7's FUNC5 being PDM_CLK0 and should be marked PDM_CLK1,

and in the config tools' Pin Perspective : the DMIC0's CLK0 has 3 routable pins (including PIO0_7) while CLK1 only has 1 available pin : P0_7 should be routable to CLK1.

Hope this can help, and that it can be fixed in future revisions of the LPC553x Datasheet.

Regards,

OE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I can confirm that I saw this misspelled and inconsistencies.

- kPLL1_to_DMIC = MUX_A(CM_DMICFCLKSEL, 2), /*!< Attach PLL1 to DMIC. */ [SDK]

- RM mentions PDM_CLK01 (and PDM_CLK02 ?) on Figures 257 to 259, as well as in the note at the beginning of chapter 45.1.3, but everywhere else only mentions PDM_CLK0 and PDM_CLK1, as well as the Datasheet which only mentions those last two.

I couldn't confirm the following; I did not find in the RM and Datasheet the [PDM_CLK23, PDM_DATA23], Could you explain this with more details? please. Do not assume anything let me review the information.

- RM mentions a few times in IOCON chapter its embedded Pinout Spreadsheet, in which pins are called PDM_CLK01, PDM_DATA01, PDM_CLK23, and PDM_DATA23.

Let me review the next question with your complete information.

- There is also ambiguity on the possibility of muxing two PDM streams on both edges through a single PDM_DATA input pin which according to RM's Figure 259 seems to be possible,

but with the issue stated above as well as the fact that the PDM_DATAn pins can seemingly only be connected to one DMIC channel, I'm not sure about this. - Would it be possible to get some clarifications for those pin routing and functionality ambiguity ?

I'm using the Datasheet Rev. 1.0, 04/2022 and Reference manual Rev. 1, 04/2022.

I look forward to receiving your comments,

Pavel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thanks for the reply and support.

I'm using the Datasheet Rev. 1.0, 04/2022 and Reference manual Rev. 1, 04/2022

I'm using those exact same versions.

I couldn't confirm the following; I did not find in the RM and Datasheet the [PDM_CLK23, PDM_DATA23], Could you explain this with more details? please. Do not assume anything let me review the information.

The [PDM_CLK23, PDM_DATA23] aren't in the Datasheet nor in the RM, but in the file Pin_Function_Table_Non_secure_MM.xlsx which is attached in the RM pdf file (and is mentioned in the IOCON chapter as reference for pinout details).

Would it be possible to get some clarifications for those pin routing and functionality ambiguity ?

Concerning RM's Figure 259 : after some experimentation on the EVK and re-reading the Figure, it's clear that it's only possible to share the CLK pin but not the DATA pin.

The fact that the Figure mentions 2 pins (CLK and DATA) which are not on the chip boundary red dotted line did mislead me.

Maybe it was meant to mention 3 pins (1CLK and 2DATA) on chip boundary which would make more sense?

Through experimentation with the LPC5536-EVK I can confirm that the pin P0_7 is actually only connectable to DMIC's Channel1 CLK (and not Channel0 CLK), as mentioned in my previous message.

Regards,

OE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thanks for all this information I will make a report when I have more information I will give you feedback.

Best regards,

Pavel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The inconsistencies were reported.

I've confirmed that the configuration is possible. The important aspect to consider is that each channel is going to be configured on a different edge for writing and the MCU will read the opposing edge for each channel. Each DMIC has a pin select to configure the edge that it will write on.

As far as the configuration seen on the figure, this is correct CH0 will provide the clock and CH1 will share same clock and frequency, then data line is also shared but as mentioned they will be on different edges.

Best regards,

Pavel