- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- MCU Bootloader

- :

- a problem when using bootloader

a problem when using bootloader

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

a problem when using bootloader

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Download the bootloader project and the APP project to 274and debug the APP through the attach function.

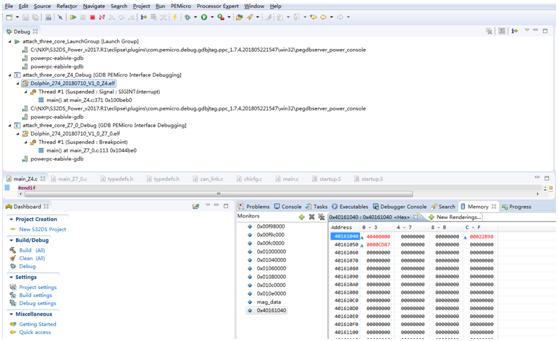

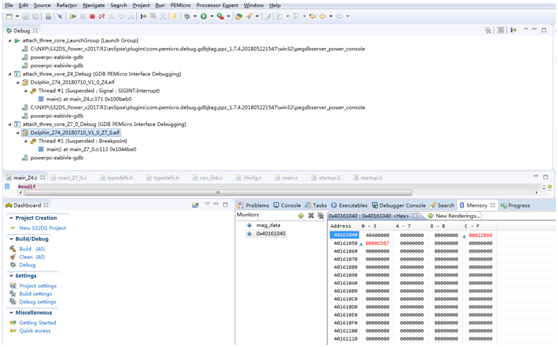

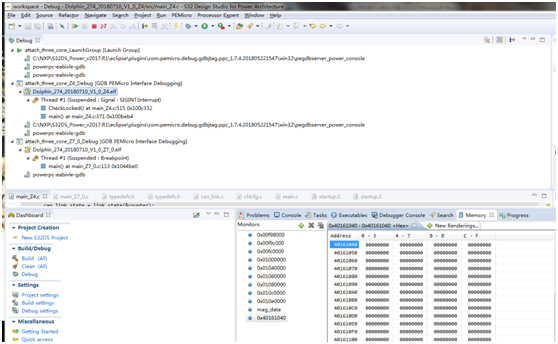

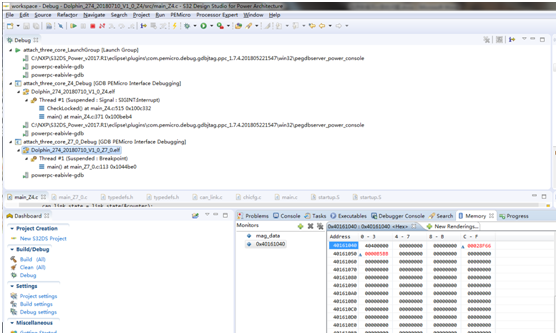

The content of the test is , pause the two cores, and then view the data in the same SRAM region in the two cores. The results are as follows.

1、when the radar detected object

1)、view in Z4 core

2)、view in Z7_0 core

the data in the pictures above are the same.

2、when the radar detected no object

1)、view in Z4 core

2)、view in Z7 core

the data in the same address are different.

Conclusion:

from the point of view of the phenomenon, when there are bootloader project and APP project in the 274chip, when the radar does not detect the target, the data are different in the same SRAM region. In fact, it is only when the same SRAM region data is different between the two cores that the radar cannot detect the target (the Z7 core has target data after processing, but there is no such data in the Z4 core.Therefore, there is no target report after Z4 core processing).

Question: Why is it that viewing the same memory area in both cores results in different data? What caused it?

If anyone knows the reason, please tell me,thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

what about cache memory? Have you tried to disable cache memory or set the area as cache inhibited? SMPU can be used to set area as cache inhibited. You can reuse some code from:

Example MPC5748G SMPU initialization GHS614

or

Example MPC5748G SMPU initialization + Process ID test GHS614

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your suggestion and the answers before, i'll reserch the problem with your advice these days.

thanks again!

Regards,

Xufei