- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- レイヤースケープ

- :

- LS1046A does not detect USB stick

LS1046A does not detect USB stick

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LS1046A does not detect USB stick

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi community,

This post echoes this one which already gave a lot of answer: https://community.nxp.com/t5/Layerscape/LS1046A-can-not-detect-USB-device-on-u-boot/m-p/1561319#M114...

The issue:

We have a LS1046A based board, it includes one USB 2.0 plug on which we try to connect a USB stick, without success so far.

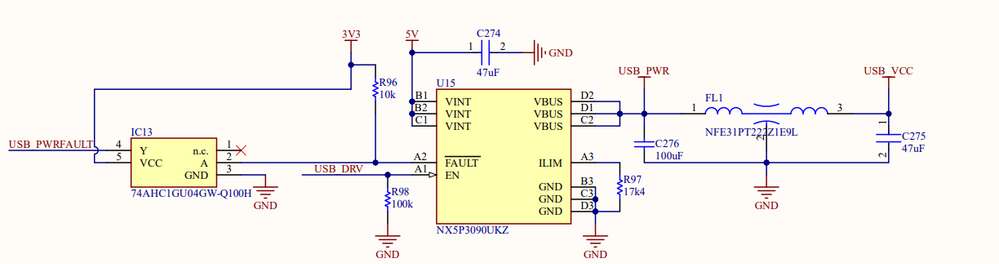

After investigating it seems that the USB_DRVVBUS signal never goes high, thus preventing the 5V (USB_VCC) from reaching the USB stick. Messing around with the RCW we managed to set this signal as GPIO and to force it up which brought the 5V to the USB plug, thus validating the "usb power circuitry" on U15, but still no device is detected regardless if it's powered or not.

Schematic for USB plug side:

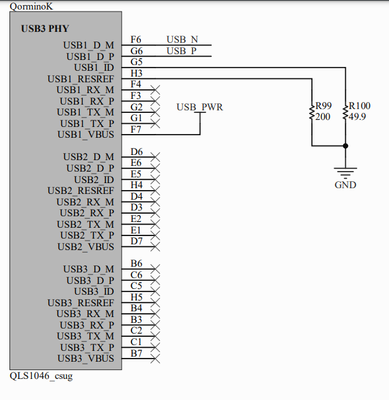

Schematic for LS1046A side :

Details about the setup:

- no SYSCLK is available, PBI modified to clock USB PHYs through DIFF_CLK

- USB PHYs are not in reset, command "md 1570418" in UBOOT reads 0x9E000000 0x9E000000 0x9E000000 ...

- USB_N & USB_P are flipped, flipping those on a ref design from NXP still showed activity on the USB port even if it was 99% errors. We made a custom cable to flip them back.

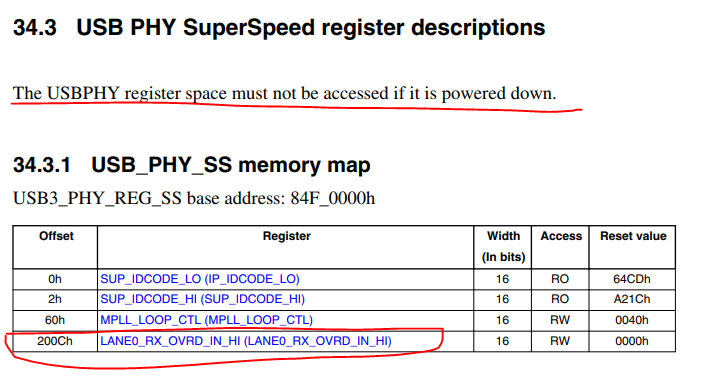

- My software guy had to remove erratum_a009007 inside the soc.c (from uboot or the linux distro, not sure about that one) system wouldn't boot otherwise. That erratum is linked to USB3 configuration, doc says no write in the linked registers should happen if USB core is powered down

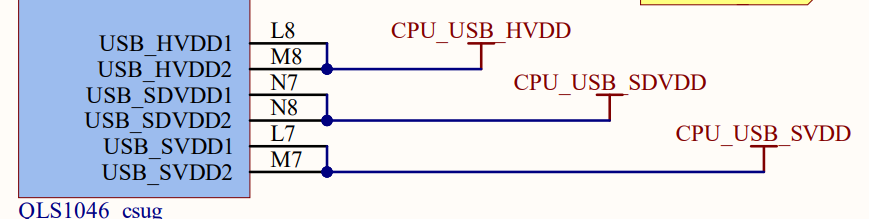

- USB power rails OK, they all go up within a 17ms delay:

- There is a history of CPU_VDD being as high as 11V (eleven volts) for short periods of time during the PCB bring-up

Some questions:

- Can I debug that issue entirely through UBOOT ? or there is a need for a linux layer to properly set things up

- Is there a way to make sure USB core is properly powered?

For the rest we are running out of juice in finding consistant leads, any help much appreciated, I can also update the setup details upon request should there need more informations.

Thanks in advance !

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

USBx_PWRFAULT,USB_DRVVBUS,USBx_PWRFAULT.

Check the three signal include rcw config and checklist requirment.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Checking the schematics, USBx_RX_P and USBx_RX_M should be grounded. I enclosed the design check-list for LS1046A. Check the Table 4 for USB power supply filter circuits.

I do not know what could be the cause "My software guy had to remove erratum_a009007 inside the soc.c (from uboot or the linux distro, not sure about that one) system wouldn't boot otherwise.". From the Dermiste_3, all USB power is connected. Can you confirm all these USB supplies are powered up when A-009007 workaround is implemented. Having said that, you do not need A-009007 as USB 3.0 is not implemented on your system.

Yes, you can debug this issue entirely under uboot. Actually, it is easier to do it under uboot.

As long as all the 3 USB power supplies are provided, the USB core should be properly powered. The USB clock can use either single ended or differential clock Sysclock. However, it has to be 100 MHz.

You can use a USB protocol analyzer to see whether any actions or packets are sent out and what wrong information is on the line. However, you need to get USB power and clock correct first.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes I am aware that RX_P & RX_M should be grounded, which is not implemented on my schematic.

I can confirm that the USB power goes up within 17ms after CPU_VDD goes up, I assume that when soc.c is executed USB cores are therefore powered.

I am not sure however if the USB core is not damaged and at this point I'm interested in seeing how I can debug this from uboot, if the core is damanged or not powered it means I won't be able to write any register linked to USB PHY, correct? Writting reg using rw should therefore not work?