- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC804 - PWM pulse generation

LPC804 - PWM pulse generation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

We need to generate the PWM with clock period of 500ms with duty cycle of 50%. Here we configured the register as per the datasheet, which are as follows

SYSCON->SYSAHBCLKCTRL0 |= 1 << 25 ;

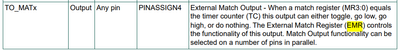

SYSCON->PRESETCTRL0 |= 1 << 25; SYSCON->SYSAHBCLKCTRL0 |= 1<<7; SWM0->PINASSIGN.PINASSIGN4 = 0X00000000; SWM0->PINASSIGN.PINASSIGN4 = (0X18) << 24 ;//0X18;// P0_24 PIN SELECTED SYSCON->SYSAHBCLKCTRL0 &= ~(1<<7); //DISABLE clock for switch matrix. CTIMER->TCR |= 1 << 1; CTIMER->PR = 0X00; CTIMER->MCR |= 1 << 9 | 1 << 10 | 1 << 27 | 1 << 0 | 1 << 1; CTIMER->MR[3] =10000; CTIMER->MSR[3]=10000; CTIMER->MR[0] =5000; CTIMER->MSR[0]=5000; CTIMER->PWMC |= 1<<3; CTIMER->TCR |= 1<<0 ; while(1);

This is the code which we developed. But there is no difference in pin status. We use

P0_24 for this PWM generation.

We not get the point of exact usage of EMR, Match shadow register.

Kindly navigate us to move further

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Dhaya

Based on the code you provided, it seems you are trying to generate a PWM signal with a 50% duty cycle and a 500ms period using the LPC804's CTIMER. I noticed a few issues in the code that might be causing the problem:

- First, make sure to enable the clock for the CTIMER block by setting the corresponding bit in the SYSAHBCLKCTRL0 register:

SYSCON->SYSAHBCLKCTRL0 |= (1 << 25);

- Next, you need to configure the CTIMER's PWM channel 3 to generate the PWM signal. You can do this by setting the appropriate bits in the PWM Control Register (PWMC):

CTIMER->PWMC |= (1 << 3);

- Lastly, you should configure the Match Control Register (MCR) to reset the timer on match with MR3 and set the PWM output on match with MR0:

CTIMER->MCR |= (1 << 10) | (1 << 0);

With these changes, your code should look like this:

SYSCON->SYSAHBCLKCTRL0 |= (1 << 25); SYSCON->PRESETCTRL0 |= (1 << 25);

SYSCON->SYSAHBCLKCTRL0 |= (1 << 7); SWM0->PINASSIGN.PINASSIGN4 = 0X00000000; SWM0->PINASSIGN.PINASSIGN4 = (0X18) << 24; SYSCON->SYSAHBCLKCTRL0 &= ~(1 << 7);

CTIMER->TCR |= (1 << 1); CTIMER->PR = 0X00; CTIMER->MCR |= (1 << 10) | (1 << 0);

CTIMER->MR[3] = 10000; CTIMER->MR[0] = 5000;

CTIMER->PWMC |= (1 << 3); CTIMER->TCR |= (1 << 0);

while (1);

However, this code will generate a PWM signal with a 20ms

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Dhaya,

Could you please take a look at LPC804 SDK's CTIMER PWM examples? It might be useful to develop your code.

We not get the point of exact usage of EMR, Match shadow register.

LPC804 User Manual. Chapter 16: LPC804 Standard counter/timer (CTIMER) explains both registers:

[LPC804 User Manual. Chapter 16. LPC804 Standard counter/timer (CTIMER). Section 16.5. Pin description]

As User Manual mentions the EMR controls whether the P0_24 is going to toggle, go low, high or do nothing when a match occurs between the TC and MR[3:0]. Section 16.6.10 of the User Manual explains how to configure the EMR.

About the MSR, User Manual's Section 16.6.13. Match Shadow Registers mentions: "The Match Shadow registers contain the values that the corresponding Match Registers are (optionally) reloaded with at the start of each new counter cycle."

The MSR could be used when you have to monitor the value of the CTIMER, for example, if you want to use it to generate a periodic event. The value of the timer could be read at any time by reading the value of the Match Shadow Register. In the example recommended it is not used to generate a PWM signal.

Best regards, Raul.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Dhaya

Based on the code you provided, it seems you are trying to generate a PWM signal with a 50% duty cycle and a 500ms period using the LPC804's CTIMER. I noticed a few issues in the code that might be causing the problem:

- First, make sure to enable the clock for the CTIMER block by setting the corresponding bit in the SYSAHBCLKCTRL0 register:

SYSCON->SYSAHBCLKCTRL0 |= (1 << 25);

- Next, you need to configure the CTIMER's PWM channel 3 to generate the PWM signal. You can do this by setting the appropriate bits in the PWM Control Register (PWMC):

CTIMER->PWMC |= (1 << 3);

- Lastly, you should configure the Match Control Register (MCR) to reset the timer on match with MR3 and set the PWM output on match with MR0:

CTIMER->MCR |= (1 << 10) | (1 << 0);

With these changes, your code should look like this:

SYSCON->SYSAHBCLKCTRL0 |= (1 << 25); SYSCON->PRESETCTRL0 |= (1 << 25);

SYSCON->SYSAHBCLKCTRL0 |= (1 << 7); SWM0->PINASSIGN.PINASSIGN4 = 0X00000000; SWM0->PINASSIGN.PINASSIGN4 = (0X18) << 24; SYSCON->SYSAHBCLKCTRL0 &= ~(1 << 7);

CTIMER->TCR |= (1 << 1); CTIMER->PR = 0X00; CTIMER->MCR |= (1 << 10) | (1 << 0);

CTIMER->MR[3] = 10000; CTIMER->MR[0] = 5000;

CTIMER->PWMC |= (1 << 3); CTIMER->TCR |= (1 << 0);

while (1);

However, this code will generate a PWM signal with a 20ms