- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: LPC5506 SCB AIRCR SYSRESETREQ bitmask sets RAM to 0

LPC5506 SCB AIRCR SYSRESETREQ bitmask sets RAM to 0

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi!

I am currently working with an LPC5506. When __NVIC_SystemReset() is called a certain SRAM0 addres range is set to 0. I have observed this happens, at least in the 0x2000_1740 -0x2000_17BF range.

This does have nothing to do with zero fill the bss segment in the ResetISR() function, since our application does not initialize the bss section (this is done intentionally).

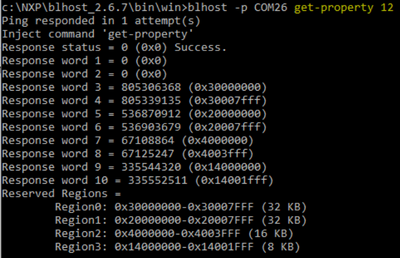

I have read the boot code in ROM may change the SRAM data. Therefore, I have used blhost to check property 12. The whole range 0x2000_000 – 0x2000_7FFF is mentioned (32 kB). However, I have observed that only certain addresses are set to 0.

Our application initializes most of the variables after a reset (no matter whether a SW reset, POR, etc.). However, there’s certain data we want to preserve on a SW reset. We're aware of the RTC general purpose registers, however, we would like to preserve more than 32 bytes of data. Are there any other means of doing this? Has someone experienced the same issue?

Thanks in advance.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

the LPC5506 has 96k of RAM in total (I know, including SRAM X). Have you tried using SRAM 1,2 or 3 (i.e. a RAM address between 0x30008000 and 0x30013FFF)?

As I will have to do the same programming in a short while I had that in the back of my mind, thus I am curious.

Regards,

Clemens

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello embeddeddavid ,

Yes, some RAM memory are reserved by ROM initialization.

About the ROM reserved regions , you can obtained from the blhost command "get-property 12":

BR

Alice

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Clemens,

As you can see in the attached image, the code in ROM also reserves SRAM 1, 2 or 3 for its own use. We are also developing some applications for a LPC55S69 and we have not experienced this issue even though the ROM bootloader theoretically also reserves the RAM. It is kind f a lottery. It would be desireable to achieve some certainty instead of trial and error.

Regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

hmm, can't see that. In the attached image it claims:

0x300000000 - 0x30007ffff (SRAM 0, secure access)

0x200000000 - 0x20007ffff (SRAM 0, non-secure access)

0x40000000 - 0x40003fff (SRAM X, non-secure access)

0x140000000 - 0x140001fff (part of SRAM X, secure access)

I do not see SRAM above 0x20008000 being claimed.

(Referring to UM11424, Rev. 1.3, Ch 2.1.5)

Am I missing something?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Nope, Clemens, you are totally right. I misled the memory addresses.

I will ask my colleagues if this might be an option.

Thanks a lot.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

the LPC5506 has 96k of RAM in total (I know, including SRAM X). Have you tried using SRAM 1,2 or 3 (i.e. a RAM address between 0x30008000 and 0x30013FFF)?

As I will have to do the same programming in a short while I had that in the back of my mind, thus I am curious.

Regards,

Clemens

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have same question and didn't get satisfied solution.