- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC1778 ethernet MAC reset Issue

LPC1778 ethernet MAC reset Issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC1778 ethernet MAC reset Issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello LPC,

I am trying to imitate RESET in Ethernet MAC but it is hanging in some condition.

................start Ethernet reset......................................................................

Chip_Clock_EnablePeriphClock(SYSCTL_CLOCK_ENET); ENABLE CLOCK PERIPHERAL - WORKS FINE PCONP

for (i = 0; i < 10000; i++) {}

GpioSet(ENET_RST_EN_OUTPUT); RESET PHY ETHERNET - WORKS FINE

for (i = 0; i < 10000; i++) {}

GpioClear(ENET_RST_EN_OUTPUT); RESET PHY ETHERNET - WORKS FINE

for (i = 0; i < 10000; i++) {}

GpioSet(ENET_CLK_EN_OUTPUT); ENABLE CLOCK FOR PHY ETHERNET - WORKS FINE

for (i = 0; i < 1000; i++) {}

LPC_EMAC->MAC.MAC1 = ENET_MAC1_RESETTX | ENET_MAC1_RESETMCSTX | ENET_MAC1_RESETRX | ENET_MAC1_RESETMCSRX | ENET_MAC1_SIMRESET | ENET_MAC1_SOFTRESET; WORKS FINE

LPC_EMAC->CONTROL.COMMAND |= ENET_COMMAND_REGRESET; WORKS FINE

LPC_EMAC->MAC.MAC1 |= ENET_MAC1_PARF; HANGS HERE ??????

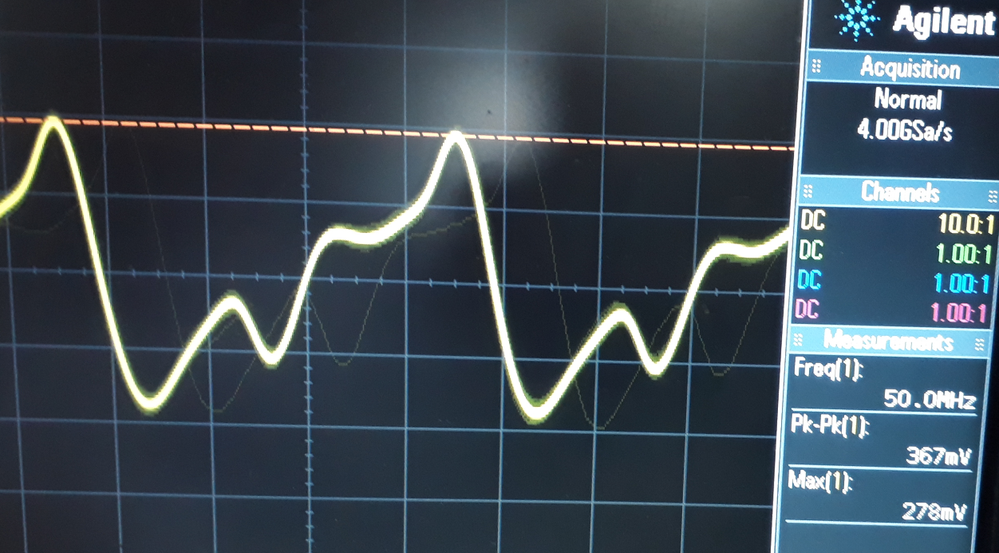

I Have checked the ENET_REF_CLK on scope, The value it is showing as 50 MHZ as i am using RMII.

I guess it is correct.

Regards,

Ashish

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ASHISH G ,

To provide the fastest possible support, I'd highly recommend you to refer to the EMAC demo for detail.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy,

Thanks for the reply.

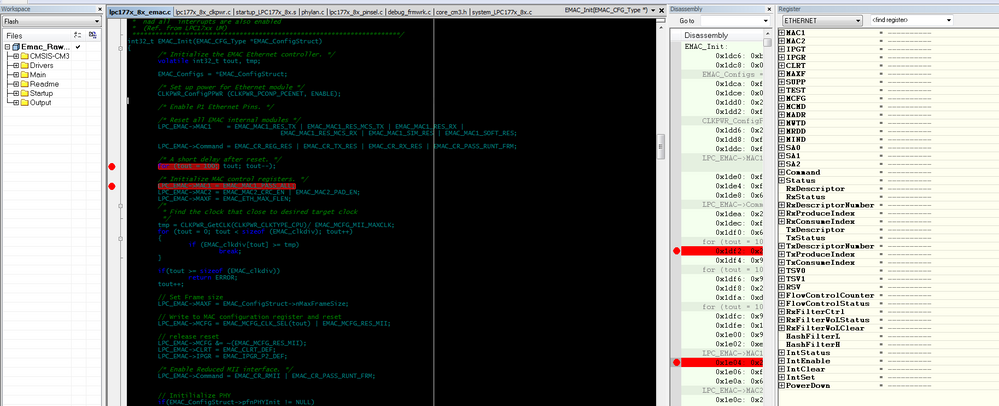

I tried to load you project to my board via IAR Jlink SWD & use debugger to check, But same issue i am facing.

I ahve changed to IAR to LPC1778 controller.

LPC_EMAC->Command = EMAC_CR_REG_RES | EMAC_CR_TX_RES | EMAC_CR_RX_RES | EMAC_CR_PASS_RUNT_FRM;

/* A short delay after reset. */

for (tout = 100; tout; tout--);

/* Initialize MAC control registers. */

LPC_EMAC->MAC1 = EMAC_MAC1_PASS_ALL; HANGS HERE ??????

Screenshot :

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ASHISH G ,

Thanks for your reply.

In order to dig deeper, I was wondering if you can share the SCH of the board and tell me the external PHY chip your use.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy,

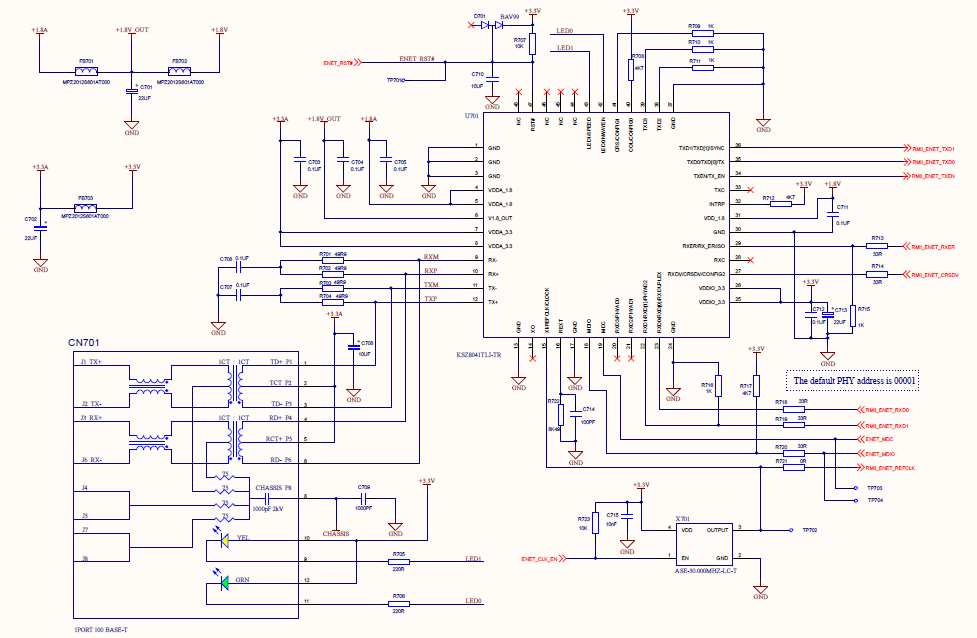

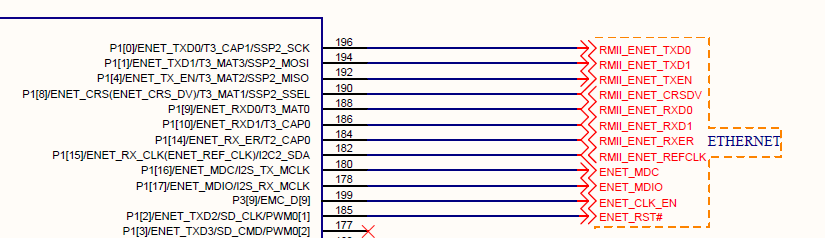

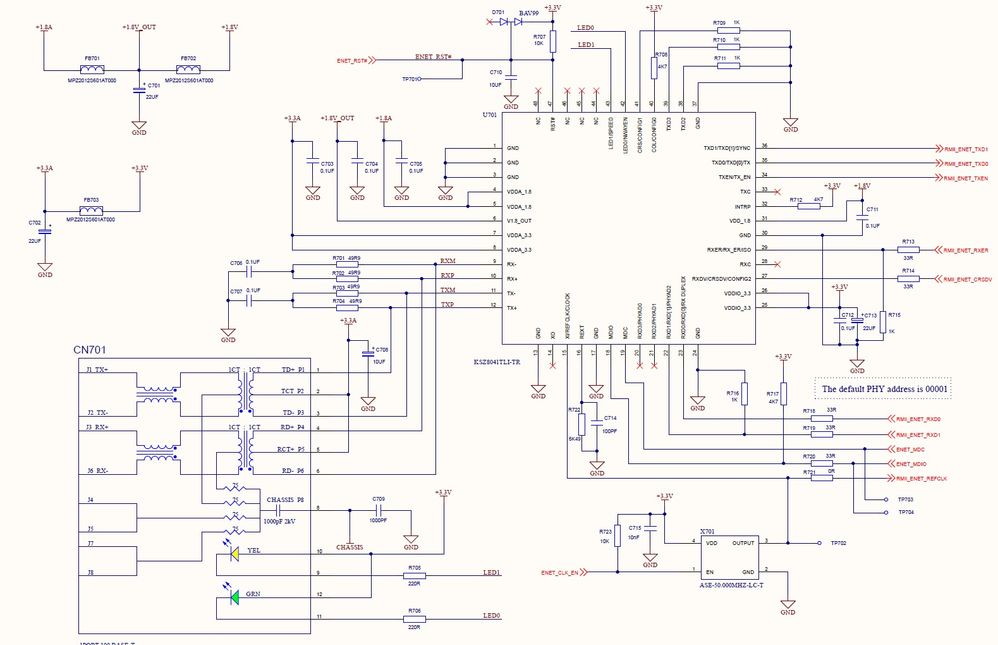

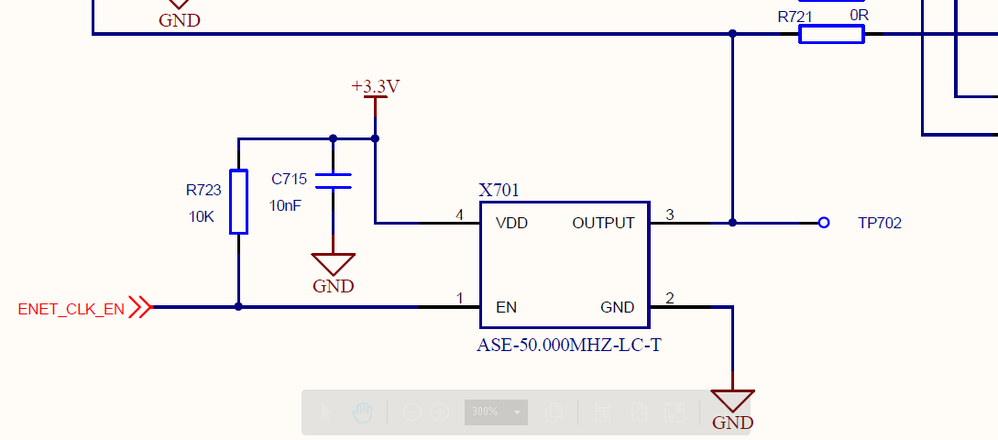

I am interfacing LPC1778FBD208 with MICREL PHY KSZ8041TL over RMII only.

I also tried to run "lpcopen_2_10_keil_iar_ea_devkit_1788.zip" examples over IAR & JLINK setup to my board.

Only Ethernet example is not running (same issue) but other examples (I2C, SPI, DMA,UART) all are running .

Note : Also As soon as look into ETHERNET REGISTERS in WATCH WINDOW during J-LINK Debug mode, it also hangs as well.

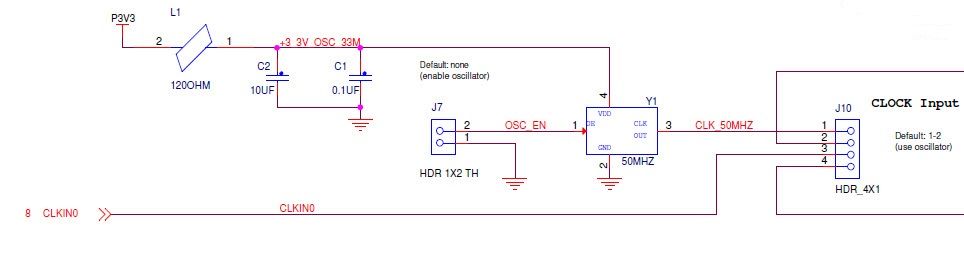

Here is the schematic :

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ASHISH G,

Thanks for your reply.

According to the description of this issue, the weird phenomena has already happened before initializing external PHY chip which is KSZ8041TL in your design, in another word, the Ethernet module which is used to handle the MAC level fails to complete the initialization process.

It's seems like a tricky problem, so I'd like to know whether this phenomena also occur in other prototypes.

Another requirement, the screenshot is not clear, whether you share a PDF of sch.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy,

I have checked in 2 prototype boards, same issue is coming. The default configuration is 100 base T for PHY

Here is the more clear screenshot

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Thanks for reply.

Two suggestion:

1. Confirm with the Microship for checking circuit design.

2. The reset state of pins of LPC1778 is high, as internal pull-up resistor enabled. In your design, the ISO pin is used to enable ISOLATE mode, so I suspect that the ISO pin is pull-up during power-up, please checking it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy,

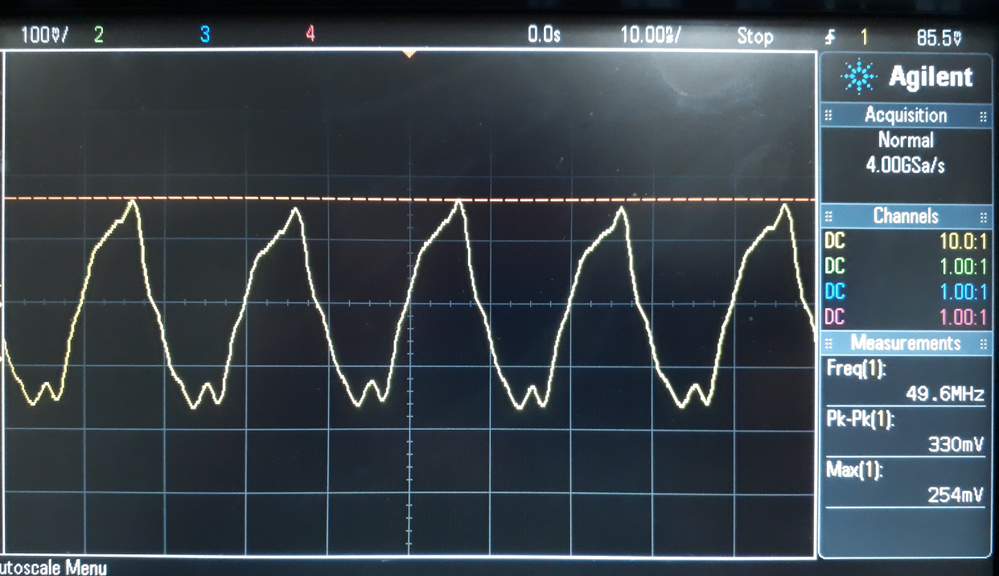

As looking at the REF_CLK 50MHZ the Pk-to Pk is 367 mV & Max is 278 mV.

Can you please check if this is the correct clock or i have to change something in schematic. My doubt is going to the Ref_clk issue.

Regards,

Ashish Gupta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ASHISH G,

Thanks for your reply.

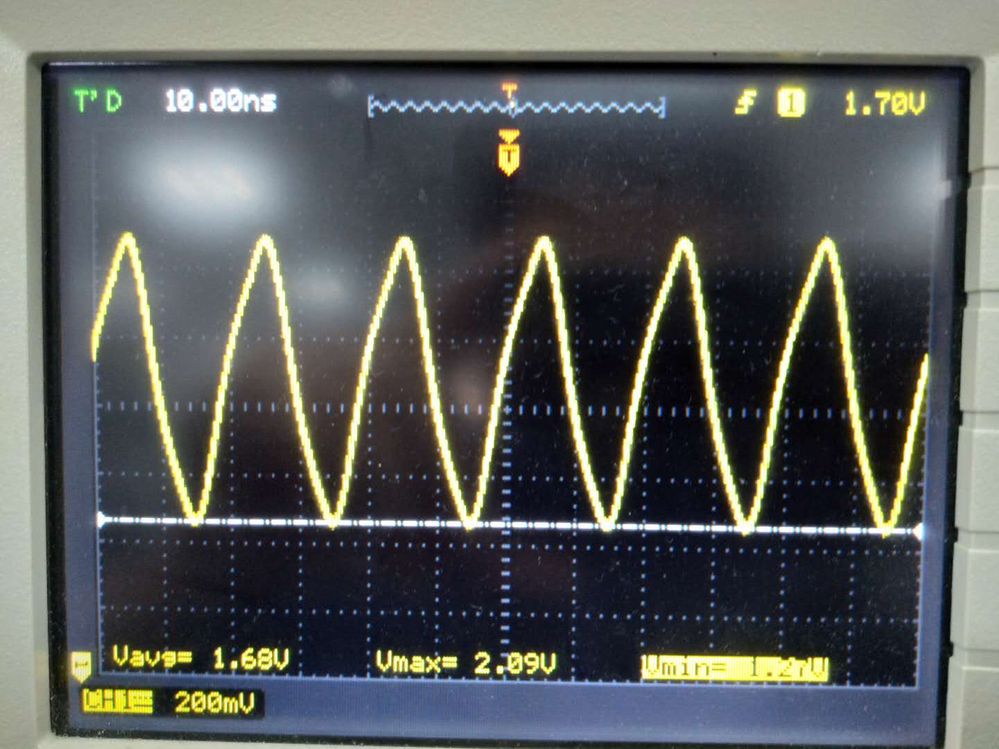

To compare with this 50 MHz clock, I've attached the Fig 1 that illustrates the output of 50 MHz oscillator in Eva board, you can see the it is standard sine wave and Pk-to Pk is 800 mV, Max is 2.09 V and Min is 1.27 V, obviously, the

clock are different with yours.

So I think it maybe the cause of issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy,

I tried to make ENET_CLK_EN pin as AD_DIGITAL, these is little ok in Clock BUT the still the Pk-to Pk is 330 mV, Max is 254mV. But issue is NOT resolved.

Are you referring to schematic of MCB1700 here for your ref clock ?

Can you suggest the part number of 50MHz crystal you are using OR Can you please suggest the reference crystal schematic for RMII for 50MHz that you have taken your 50MHz design.

Regards,

Ashish Gupta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ASHISH G,

Thanks for your reply.

The sch of external oscillator 50 MHz is from TWR-k60F120M board, and the 50 MHz oscillator is SG-210SFT 50.0000ML, EPSON, you can get the its datasheet via the following link.

https://support.epson.biz/td/api/doc_check.php?dl=brief_SG-210STF_en.pdf .

Another thing, I just received the survey of 00156754 which was created by yourself

As we have already used the community to communicate, I don's response to the case simultaneously.

However the case will be closed in 7 days if theres's no email reply.

I understand you maybe not happy with the case to be closed, while the your issue still bother you.

So I hope you can do a survey again after this issue is solved, it's important to us and thank you in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy,

I really sorry for that.

I was thinking the ticket was not related to your support forums, so did that. Your support is very helpful for me as now i am very close to issue.

Most probably it the crystal that is creating the problem. I am connecting an MCB1800 eval board crystal output pin to my prototype & check. Surely will do a good survey as issue is very close to resolved :smileyhappy:

Regards,

Ashish

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HiASHISH G,

What is going on? Is the issue solved ?

BR,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy,

The issue was with the crystal & the PCB routing connections for 50MHz crystal.

Thanks for debugging & helping me this issue. It was a great help.

Regards,

Ashish Gupta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ASHISH G,

I'm glad to hear that you had figured the root cause of this issue.

So I was wondering if you can redo a survey of the case: 00156754.

It's important to us and thank you in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ASHISH G,

Thanks.

If you have any further questions, please feel free to contact with me.

BR,