- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- What happens when an interrupt occurs? (KV10 - Thumb Processor)

What happens when an interrupt occurs? (KV10 - Thumb Processor)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What happens when an interrupt occurs? (KV10 - Thumb Processor)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

More specifically where do I go to learn about what the processor does when it recognizes an enabled interrupt?

I'm using a FRDM-KV10Z so my first choice reference is the KV10 Sub-Family Reference Manual. But there's not much in there that I see about interrupts. It refers one to the ARM Cortex-M0+ Technical Reference Manual for a "full description" of the NVIC. But the full description turns out to be a few mostly blank pages with a reference to the ARMv6-M Architecture

Reference Manual. The problem here is that this document seems to be describing ARM architecture rather than Thumb architecture.

My understanding is that the KV10 is Thumb only. Assuming this to be true I'd like to know how this Thumb processor reacts when it acknowledges an interrupt. What gets saved where? Are further interrupts disabled and if they are, how can I re-enable within the interrupt handler? What does the processor do when it returns from an interrupt? Why don't I have to somehow acknowledge an interrupt?

Also please consider this disassembly of the entry point of some 'C' code I have written to process a UART interrupt:

UART0_IRQHandler:

00000648: push {r3, r4, r7, lr}

0000064a: add r7, sp, #0

165 s1 = *UART0_S1&0xaf;

0000064c: ldr r3, [pc, #96] ; (0x6b0 <UART0_IRQHandler+104>)

0000064e: ldr r3, [r3, #0]

00000650: ldrb r3, [r3, #0]

00000652: movs r2, #80 ; 0x50

00000654: bics r3, r2

00000656: uxtb r4, r3

What I see here is that four registers are being saved, but r2 is not one of them; and r2 is being modified. What is going on here?

Thanks in advance for any replies.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Look for:

DUI0662B_cortex_m0p_r0p1_dgug.pdf

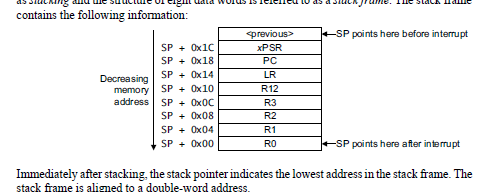

Section 2.3.6 has this automatic-stacking info:

The 'interrupts which are disabled' by the start-of-service of one interrupt are 'those at this or lower priority', enforced by the NVIC. Higher priority are still 'fully able' to interrupt an ISR unless the global-interrupt-enable is cleared [__disable_interrupts()]. Note that such manual over-ride of the automatic interrupt-hardware is NOT recommended in ISRs.

Interrupt generating devices generally have specific 'acknowledge' processes to follow, but the NVIC and following ARM hardware are 'self acknowledging'. Indeed, there isn't even a special 'interrupt return', so interrupt handles don't need 'special keywords', as a 'special code' is loaded into the Link Register (LR) to indicate the exception-processing, and recognized by hardware as part of the 'normal' return operation.