- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- OV2640: Taking a picture?

OV2640: Taking a picture?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

OV2640: Taking a picture?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

i am working with Kinetis K60F MK60FN1M0 and the OV2640 camera.

Has anyone experience with the OV2640 camera?

I connected the camera with the microcontroller. I generated a XCLK signal with 10.5 MHz. I can talk to the camera with I2C Bus. So the communication works. But i get no VSYNC signal.

Have i to start taking picures? For example, something like "get Picture = ON". I did not find a command like that in the register of the OV2640 camera.

i read that the camera automatically generate the VSYNC, HREF and PCLK signals if it gets the XCLK signal.

If that is true, then why i do not get a VSYNC signal?

Did someone work with the OV2640 camera?

Maybe someone can tell me how i get the VSYNC, HREF and PCLK signals.

Best Regards

Armend

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Armend,

I used an Ov7670 because is the only camera model that I have here, I Used an oscilloscope and the project that i redirected to you in this question Camera + Kinetis . I debugged by step till the initialization of the camera, and the sync signals appear in this step. please check if you are giving the right XCLCK value, or please send me your project maybe I can find what is going on by watching your code.

here is a post that helped me a lot with the camera. its for the Ov7670 but have some theory that might be useful.

Hope this helps.

Have a great day.

Best regards.

Jonathan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonathan,

thank you for your help.

I have looked at the demo that you dent me. But i could not find the starting point when the camera start to take a pciture.

I will continue looking at the demo. Maybe i will find some hint or something like that.

In my project i am using the following components:

- A I2C component to communicate with the camera. I tried it and that works very fine.

- A PWM component to generate a PWM signal with 30 MHz (before it was 10.5 MHz) and a duty cilce of 50% (according to the datasheet i need a PWM with at least 6 MHz, so with 30 MHz i should be safe).

- A GPIO component for the hardware reset. There is a pull up resistor.

- A other GPIO component for the VSYNC signal. For the microcontroller its a input signal with no pull up or pull down resistor

In the main.c function i wrote this code:

WAIT1_Waitms(4);

PTC_Init(); //hardware reset init function. The initial value is 0. So the camera will get a reset signal (all registers are set to //default)

WAIT1_Waitms(3);

PWM1_Init(NULL); //PWM init function. The camera will get the XCLK signal (its a pwm signal with 30 MHz and 50% duty cicle)

WAIT1_Waitms(4);

GPIO_PDD_SetPortDataOutput(PTC_DEVICE,(1<<14)); //Now the hardware reset value is 1. The camera will no get a reset signal //anymore

WAIT1_Waitms(4);

PTA_Init(); //Port A init function to get the VSYNC signal from the camera

The I2C compnent i did not use because first of all i will only get the control signals (i.e. VSYNC). So i can use the default values in the register of the camera.

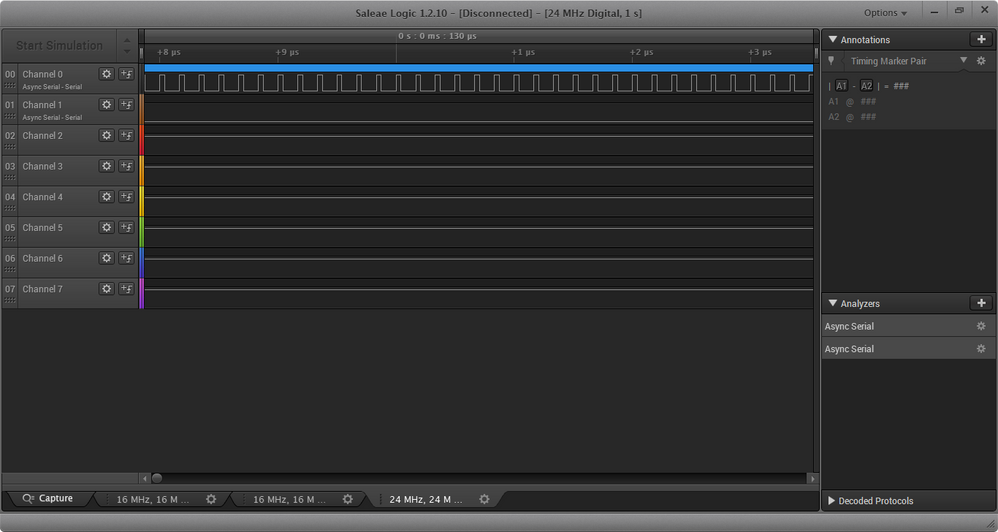

Then i looked the XCLK and the VSYNC signals with a logic analyzer:

Channel 0 is the XCLK signal. Channel 1 is the VSYNC signal.

As you can see the XCLK signal is a rectangle signal. But the VSYNC signal is always zero.

That means the camera did not generate a VSYNC signal.

According to the Datasheet of OV2640, the XCLK signal have to be at least 6 MHz. 24 MHz are recommended.

According the default values in the register of OV2640 the clock divider is 1. So the clock divider can not be the problem.

And i read that with the default values the frequency of PLCK will be the same as the frequency of XLCK. And with clock divider 1 it has to be 30 MHz.

I would send you my project but there is no attachment button or something like that.

But maybe you can give me a mail address and i will send you my project as a mail.

Best Regards

Armend

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jonathan.

I found the problem. My PWM_Component do not generate a PWM signal. A PWM signal is a rectangle signal.

At my University i controlled the XCLK signal (coming from my PWM_Component) with a oscilloscop and the XCLK signal is like a Sine - Signal.

According to the datasheet of OV2640 it has to be a rectangle signal (in the datasheet i read: "Clock input rise/fall time = max. 5ns").

So that means i have to create my PWM signal with a other CodeWarrior Component.

Maybe you can tell me how i can generate a PWM signal (= rectangle signal with fall/rise time max. 5 ns) with a frequency of 24MHz and a duty cycle of 50%.

I am working with Kinetis K60F MK60FN1M0.

Best Regards

Armend