- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: MKS22 SPI1 module DMA for TX and RX

MKS22 SPI1 module DMA for TX and RX

I'm trying to use multiple DMA channels to fill PUSHR and empty POPR on _both_ SPI modules of an MKS22.

SPI0 is working fine but SPI1 is not behaving as expected.

If I only use DMA to fill PUSHR, that works fine.

I noticed that the MKS22 only has one DMA request line for SPI1 so it looks like it isn't possible to use DMA for both TX and RX for SPI1. Is that right? Is there a workaround?

已解决! 转到解答。

Hello,

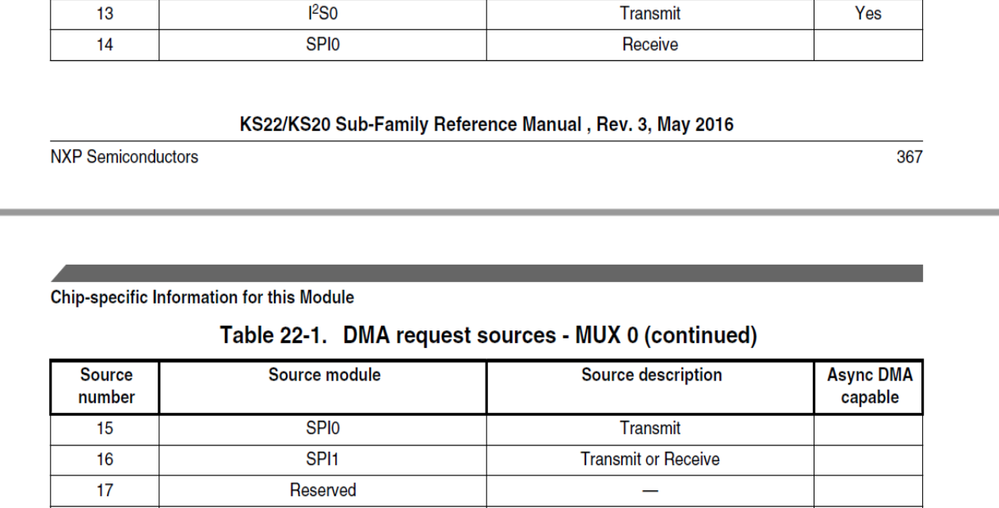

Your understand is correct. From the reference manual, Table 22-1, there listed that SPI0 use dedicated DMA source numbers for TX and RX. However, for SPI1, the DMA source are shared( Transmit or Received).That is the reason why your situation is.

There is a work-around. This is hinted in the DMA multiplexer "Chip Configuration" section of the controller's reference manual, but the manual doesn't go into detail.

If you have a PIT timer available:

1. Perform receive side setup in the same manner as for SPI0.

2. Set up the transmit side DMA on channel 0..3 depending on the PIT timer channel to be used. Select one of the always-enabled request sources in the channel configuration register, and set the TRIG bit.

3. Configure the DMA transmit descriptor for memory-to-register transfer.

4. Set the PIT timer period. The period of the timer must be a bit longer than the SPI byte transfer time so that the transmit buffer is empty when the transmit DMA channel writes the next byte. Trial and error with an oscilloscope, or calculate it...

5. Set the SPI chip select. It mayt be possible for the SPI controller to do this, I'm doing it in code.

6. Enable the receive-side DMA transfer. Nothng happens since no SPI clocks are generated.

7. Enable the transmit-side DMA transfer. Transfer occurs.

8. Negate the chip select via interrupt callback when the transfer completes.

I'm guessing something similar works using one of the flex timer channels as trigger source, but I haven't verified that.

Thanks for the suggestion Fred. If I understand correctly, there's still an interrupt for every transfer. It's that interrupt for every transfer that I need to avoid due to the 30+ cycle overhead. I've solved my problem by interspersing SPI1 sends/reads through other predictable code patterns.

Hello,

Your understand is correct. From the reference manual, Table 22-1, there listed that SPI0 use dedicated DMA source numbers for TX and RX. However, for SPI1, the DMA source are shared( Transmit or Received).That is the reason why your situation is.