- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: KV31 ADC Sample Rate with Hardware Averaging

KV31 ADC Sample Rate with Hardware Averaging

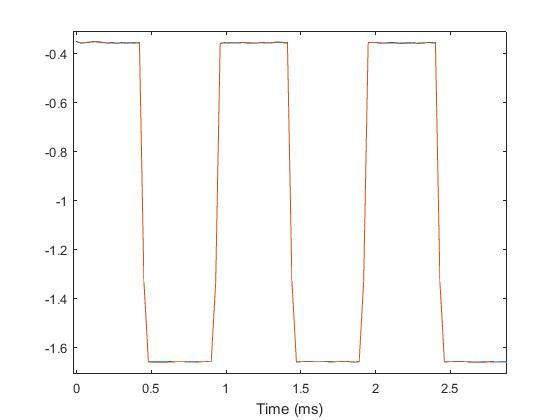

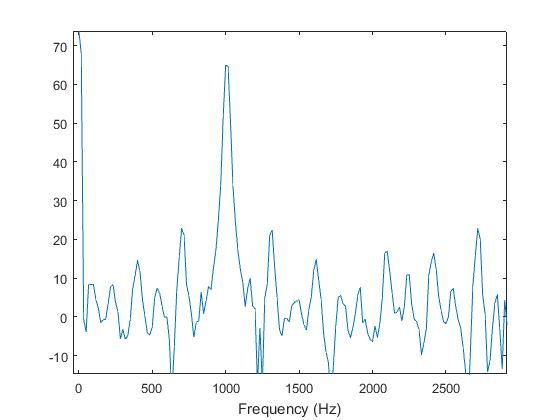

I'm using the PIT to hardware trigger the ADC module. I was able to successfully capture a 1 kHz test signal at a 100 kSPS rate. I then implemented hardware averaging. I expected the sample rate to drop to the base sample rate divided by the number of averages (i.e. 100 kSPS / 4 avg. = 25 kSPS). Instead it dropped by a factor of 3 (33.33 kSPS). I found the other settings resulted in sample rates that were (3/4 * number of avg's). So an average of 8 resulted in a sample rate reduction of 6. Has anyone else confirmed this? Is the intended behavior?

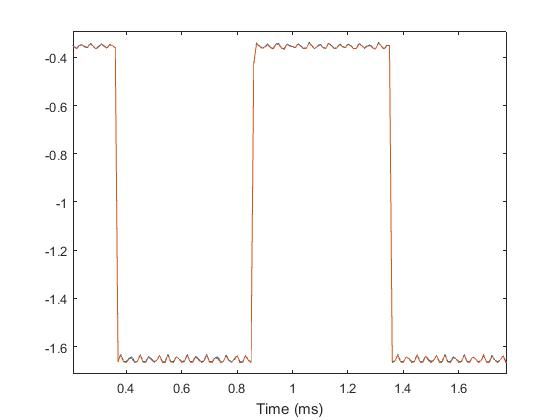

No Averaging - 100 kSPS Assumed Sample Rate, 1 kHz Test Signal

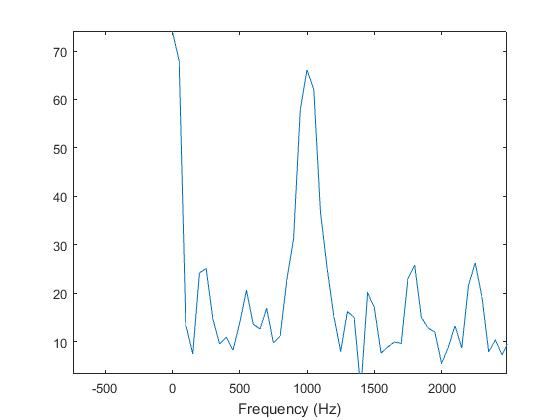

Averaging of 4 - 25 kSPS Assumed Sample Rate, 1 kHz Test Signal

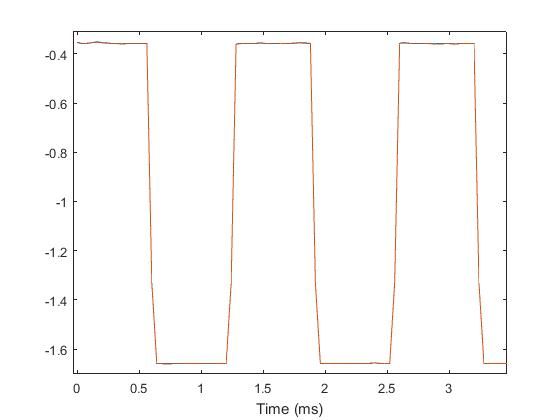

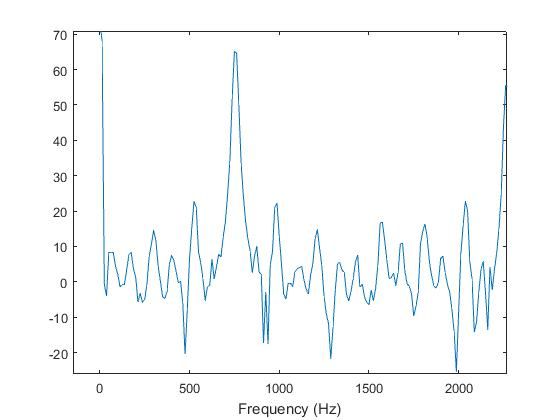

Averaging of 4 - 33.33 kSPS Assumed Sample Rate, 1 kHz Test Signal

已解决! 转到解答。

Hi!

When you are using hardware avereging your PIT just starts a burst of a conversion. Each burst consist of number of hardware averege. Inside each of burs acting rules of continios conversion.

The time of such a burst depends on your ADC clock speed, sample time settings and ADC resolution.

Hi!

When you are using hardware avereging your PIT just starts a burst of a conversion. Each burst consist of number of hardware averege. Inside each of burs acting rules of continios conversion.

The time of such a burst depends on your ADC clock speed, sample time settings and ADC resolution.

Hi Shawn Mason

Sorry for the late reply. It is difficult to us determinate the problem here if we don't have knowledge of how you setup the ADC conversions. How are you setting your sample time? and how is your Base conversion time? is it possible that you share your complete project or the part that setup your ADC conversion?

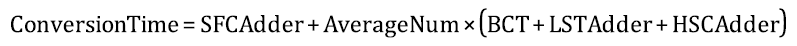

I recommend you to check section 31.4.3.5 Sample time and total conversion time in the reference manual. Here you could find:

So, ConversionTime could be affected by time added due to long sample or High-speed.

Hope this information help you, please don't hesitate to tell me if you have more question of this.

Best Regards

Jorge Alcala