- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: KV10Z 75MHz Clock

KV10Z 75MHz Clock

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

KV10Z 75MHz Clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Iv'e been playing around trying to get a KV10Z chip up and running. I have success programming and debugging with the default clock, but I noticed a few things that don't make sense to me.

1. I only have a 1k pullup on the reset pin, but a 0.1uF cap to ground is recommended. However, if I add any sort of capacitor the reset pin never goes high when powering up until the cap is removed. I've also tried a 0.01uF cap with same results.

2. How do I get the 75MHz clock going? I used the KDSDK project generator to create a blank project which I have attached. I see there is a function 'SystemCoreClockUpdate' in the startup but it never gets called. Do I need to call this somehow? There is also clock configuration details defined in the function 'SystemInit' which is called during startup.

3. I also noticed there are parts of the clock setup in the KDSK that deal with 'enableCapacitor'? What is this enabling? Does enabling it mean I don't need external capacitors?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stephen Monn

About your questions:

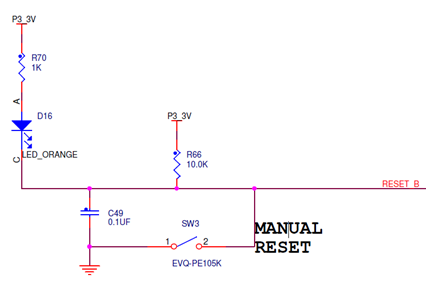

- Please check the schematic design of TWR-KV10Z3 and compare with yours, there is a manual reset part, they use a 10K as pullup and a 0.1uF capacitor from reset_b pin to ground:

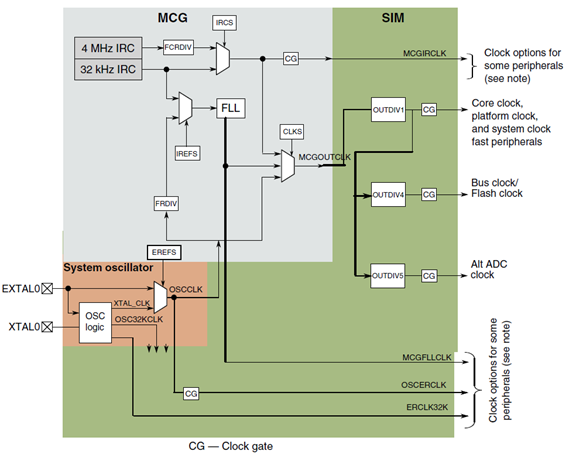

2. The configuration of the clock depend of various factors, as you can see in the below image the core clock can be configured in different modes:

For example, with ksdk, if you want to configure the clock with 75 MHz you can do something like:

clock_manager_user_config_t g_defaultClockConfigRun=

{

.mcgConfig =

{

.mcg_mode = kMcgModeFEE, // Work in FEE mode.

.irclkEnable = true, // MCGIRCLK enable.

.irclkEnableInStop = false, // MCGIRCLK disable in STOP mode.

.ircs = kMcgIrcSlow, // Select IRC32k.

.fcrdiv = 0U,

.frdiv = 3U,

.drs = kMcgDcoRangeSelMidHigh, // Mid high frequency range

.dmx32 = kMcgDmx32Default, // DCO has a default range of 25%

}

};

clock_manager_user_config_t * config= &g_defaultClockConfigRun;

CLOCK_SYS_BootToFee(&config->mcgConfig);

I recommend you to check the ksdk_1.3 example code in {PATH_KSDK_1.3.0}\examples\twrkv10z32, and the reference manual of the KV10 family. You can also check:

Change between clock configurations

how to change K64F system clock without PE?

KSDK Clock configurations and Low Power modes with Processor Expert

3. Yes, there are some internal capacitors that can be enable when you want to use an external crystal, but again all depend on how you configure your MCU.

Hope this could help

Have a great day,

Jorge Alcala

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I got the clock working at 75MHz but how can I confgure the clock to 50MHz? I understand the clock dividers in the SIM, but I don't understand the math used to figure out the clock coming from the FLL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stephen Monn

The FLL clock configuration comes from the MCG module. If you check the reference manual for KV10 in the page 479 and 480, it tell you how configure these registers to get the clock frequency that you need.

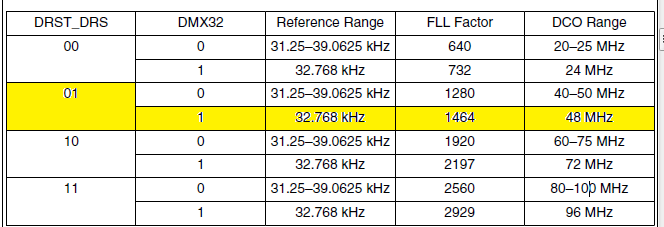

In this case the FLL is configure with the DMX32 and DRST_DRS registers. For example, to got the FLL working in 48 MHz:

Please check the reference manual and tell me if you have any more questions

Have a great day

Jorge Alcala

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------