- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- FRDM KE06Z: How to access Interrupt service program?

FRDM KE06Z: How to access Interrupt service program?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I just use Kinetis E series MCU. And use GPIO_demo code to test my board, I wanna use Interrupt service program to light LED for 1Hz. But never access the Interrupt service program, I check the demo program, and set NVIC_ISER and RTC_RTIE, this 's OK. However, dont using interrput program to lingt LED, and polling RTIF flag code is OK.

I dont kown how to access interrupt service program, THX for your Help.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scofield,

When using an Interrupt Service Routine (ISR) you have to consider next conditions:

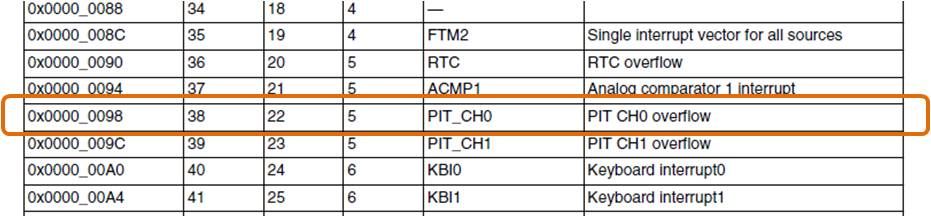

- When Configuring your Peripheral (In my case I will use PIT_CH0 as Interrupt source) you have to set the right flags to request an interrupt:

- Then, you must enable its respective vector in the NVIC module. This steps consists to write to specific ISER register and set its priority:

As you can see on Interrupt Vector Assignments table on MCU’s reference manual, PIT_CH0 vector is expressed as 38, however, when enable this vector on NVIC module, we must select IRQ value (38 – 16 = 22; It subtracts 16 because the first 16 vectors are core-vectors.)

- After NVIC configuration is done, We must enable all interrupts in the core, this is done by using the assembler instruction: CPSIE i:

/* Enable interrupts (clear PRIMASK) */

#define ENABLE_INTERRUPTS asm(" CPSIE i");

- Then, we must implement our ISR. In this ISR we must clear the specific flag that causes the interrupt request.

void PIT_CH0_IRQHandler(void) {

/* Clear Timer Interrupt Flag */

PIT_TFLG0 |= PIT_TFLG_TIF_MASK;

/* Do your ISR proccess here */

}

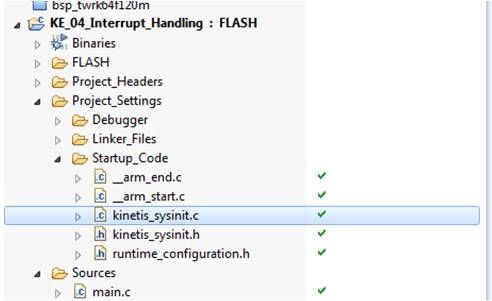

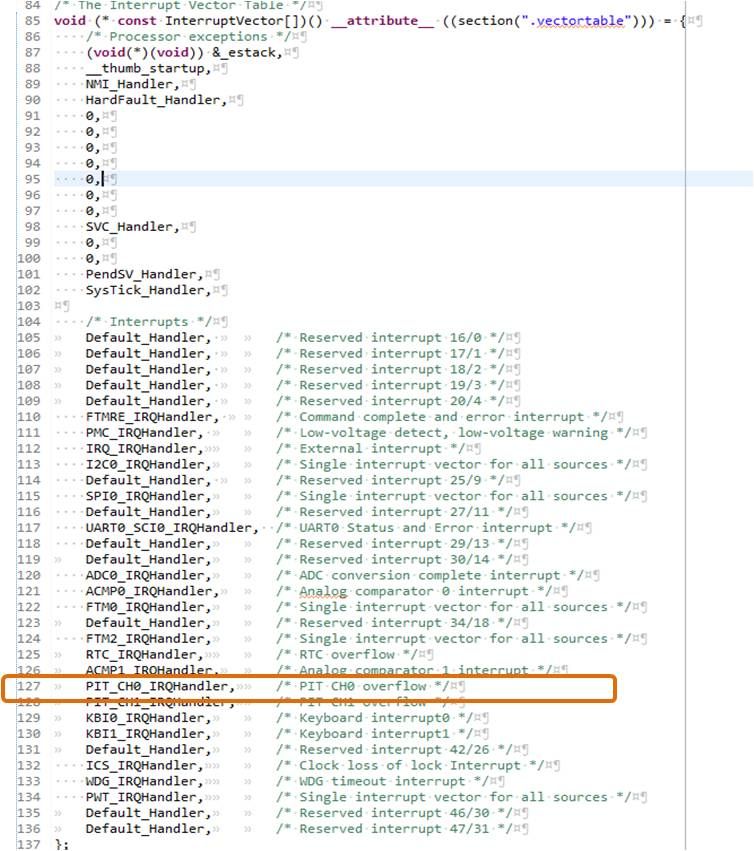

- At this point, how does the MCU knows that PIT_CH0_IRQHanlder corresponds to PIT0? Well, there is a table located at: Project_Settings > Startup_Code > kinetis_sysinit.c (for CodeWarrior 10.6 and bare metal project)

- In this source file, there is a table where all ISR are declared, so make sure your ISR is named exactly the same as in InterruptVector table:

- After following these steps you shouldn’t have any problems on attending the specific ISR.

I attached the project (It was done using a KE04 board) but hope this could serve as example.

Regards,

Isaac Avila

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scofield,

When using an Interrupt Service Routine (ISR) you have to consider next conditions:

- When Configuring your Peripheral (In my case I will use PIT_CH0 as Interrupt source) you have to set the right flags to request an interrupt:

- Then, you must enable its respective vector in the NVIC module. This steps consists to write to specific ISER register and set its priority:

As you can see on Interrupt Vector Assignments table on MCU’s reference manual, PIT_CH0 vector is expressed as 38, however, when enable this vector on NVIC module, we must select IRQ value (38 – 16 = 22; It subtracts 16 because the first 16 vectors are core-vectors.)

- After NVIC configuration is done, We must enable all interrupts in the core, this is done by using the assembler instruction: CPSIE i:

/* Enable interrupts (clear PRIMASK) */

#define ENABLE_INTERRUPTS asm(" CPSIE i");

- Then, we must implement our ISR. In this ISR we must clear the specific flag that causes the interrupt request.

void PIT_CH0_IRQHandler(void) {

/* Clear Timer Interrupt Flag */

PIT_TFLG0 |= PIT_TFLG_TIF_MASK;

/* Do your ISR proccess here */

}

- At this point, how does the MCU knows that PIT_CH0_IRQHanlder corresponds to PIT0? Well, there is a table located at: Project_Settings > Startup_Code > kinetis_sysinit.c (for CodeWarrior 10.6 and bare metal project)

- In this source file, there is a table where all ISR are declared, so make sure your ISR is named exactly the same as in InterruptVector table:

- After following these steps you shouldn’t have any problems on attending the specific ISR.

I attached the project (It was done using a KE04 board) but hope this could serve as example.

Regards,

Isaac Avila

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, I solve the problem. I set RTC interrupt exactly, but I forgot to set my ISR code to the interrupt vector. However, I take a Macro for linking my interrupt service code to interrupt vector. In the interrupt souce file, I do it as follow.

#ifndefine RTC_IRQHandler

#define RTC_IRQHandler RTC_Isr // RTC-Isr is my interrupt code.

extern void RTC_Isr(void);

Before making the Macro , I comment the RTC_IRQHandler Func. declaration.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello scofield,

I recommend you firstly refer to a GPIO interrupt demo code .

And which IDE do you use ? If CW , please refer to here :

....\Freescale\CW MCU v10.6\MCU\CodeWarrior_Examples\Kinetis_Examples\KE\build\cw\ke06\GPIO_demo

If you do not use this , i attachment the main file , i think you can refer to .

If you have some question about this demo , you can tell me !

Have a great day,

Alice

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your help. I conquer the problem.I forgot to set the Interrupt vector.