- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 製品フォーラム

- :

- ColdFire/68Kマイクロコントローラとプロセッサ

- :

- Process Expert UART Multidrop parity setup

Process Expert UART Multidrop parity setup

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Process Expert UART Multidrop parity setup

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Sir,

Processor Expert generates different registry addresses, as it was done before for UART having

#define MCF_UART_UMR_PM_MULTI_ADDR (0x1C). I need setup it for using RS485.

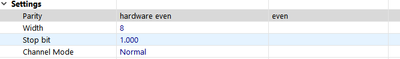

PEx creates me for UART with even parity

void AS2_Init(void)

{

SerFlag = 0x00; /* Reset flags */

/* UCR1: ??=0,MISC=3,TC=0,RC=0 */

setReg8(UCR1, 0x30U); /* Reset UART transmitter */

/* UCR1: ??=0,MISC=2,TC=0,RC=0 */

setReg8(UCR1, 0x20U); /* Reset UART receiver */

/* UMR11: RXRTS=0,RXIRQ=0,ERR=0,PM=0,PT=0,BC=3 */

setReg8(UMR11, 0x03U); /* Set the UMR1 register */

/* UMR21: CM=0,TXRTS=0,TXCTS=0,SB=7 */

setReg8(UMR21, 0x07U); /* Set the UMR2 register */

/* UCSR1: RCS=0x0D,TCS=0x0D */

setReg8(UCSR1, 0xDDU);

/* UBG11: Divider_MSB=0 */

setReg8(UBG11, 0x00U);

/* UBG21: Divider_LSB=0xF0 */

setReg8(UBG21, 0xF0U);

HWEnDi(); /* Enable/disable device according to status flags */

}

How to modify UART_UMR_PM registry to make multidrop parity?

Regards,

Marceli

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Which ColdFire product you are using? Please provide the part number.

best regards,

Mike

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike,

I am using MCF5213ACF80.

Regards,

Marceli

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

First of all, sorry for the later reply.

I could find below support record info about ColdFire(MCF5282) UART multidrop mode. Hope below info could be helpful:

MCF5282 is using the same UART module with MCF5213.

Question:

As part of my recent development effort I’m trying to configure one of the UARTs of MCF5282 in multi-drop mode. The ISR is working fine in address detection mode but only once; then onward I’m not getting the interrupts. These are the set of operations that I’m performing on the UART2 module. Initialization() { Reset RX and TX; // Reset Mode register so it points to UMR1 Aux->AuxRegs->CommandReg->Register =AUX_RESET_MODE_PTR; Aux->AuxRegs->Mode1Reg->Register = (BYTE)0|(CFAUX_PARITY_MULTIDROP_ADDR|Aux->Line.DataBits); // Disable the receiver so that it wake up when we get the next address character Aux->AuxRegs->CommandReg->Register =AUX_RX_DISABLE; Do rest of the UART initialization; } UART2ISR() { if (RxReady) { while ((RxReady)||(FIFOFull)) { Do the necessary processing; // Must read the Rx byte to clear the interrupt. // This also advances/clears the statReg bits to the values for the next queued byte. RxByte = Aux->AuxRegs->RxBufReg->RxByte; // Check if it is my own address or broadcast address if ((MY_ADDRESS == RxByte) || (BCAST_ADDRESS == RxByte)) { // Data recording mode // Reset mode register pointer before access... Aux->AuxRegs->CommandReg->Register =AUX_RESET_MODE_PTR; Aux->AuxRegs->Mode1Reg->Register = (BYTE) 0 | (CFAUX_PARITY_MULTIDROP_DATA| Aux->Line.DataBits); Aux->AuxRegs->CommandReg->Register = AUX_RX_ENABLE; } else if (MESSAGE_TERMINATOR){ // Address detection Mode ParityReg = CFAUX_PARITY_MULTIDROP_ADDR; // Reset mode register pointer before access... Aux->AuxRegs->CommandReg->Register =AUX_RESET_MODE_PTR; Aux->AuxRegs->Mode1Reg->Register = (BYTE) 0 | (CFAUX_PARITY_MULTIDROP_ADDR | Aux->Line.DataBits); Aux->AuxRegs->CommandReg->Register =AUX_RX_DISABLE; } Address: Bit9 = Set; Bit8 to Bit1 = address Data: Bit9 = Clear; Bit8 to Bit1 = Data Terminator: Bit9 = Set; Bit8 to Bit1 = 0xFF Can you please help me with this.

Answer

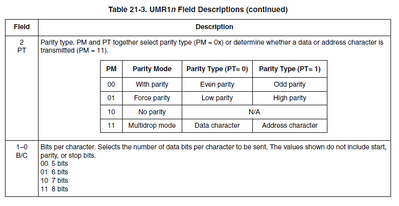

Regarding your inquiry, I am not sure if you have configured UART2 to work in interrupt mode, to do this in user_config.h you need to enable ITTYC = 1. The MCF5282 only supports 5–8 data bits plus parity. The parity bit could be used as the 9th bit. There are the UMR1n[PM; PT] bits which it is in position to set up either for Force parity, or for Multidrop mode. In multidrop mode, the address character has the 9th bit==1 and data character has the 9th bit==0 (8bit character is assumed). Any way, this will require a change in the UMR1n mode register before a character is pushed to the transmit buffer. A change in UMR1n needs to perform RESET MODE REGISTER POINTER and RESET TRANSMITTER/RECEIVER commands (UCRn command register) in advance.

About UART UMR register setting, there with below info for your reference:

Qustion: There are two registers _UMR1 and _UMR2. But the have the same ipsbar-offset!!! How should this work?

Answer: There is one pointer to UMR1n and UMR2n registers.

The UMR1n can be read or written when the mode register pointer points to it

> After Reset of CPU

> After RESET MODE REGISTER POINTER command using UCRn[MISC].

After UMR1n is read or written , pointer points to UMR2n and can UMR2n can be accessed .

UMR2n access doesn't update the pointer !

I attached related code for your reference.

Wish it helps.

Mike

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike,

To avoid complexity, Init_UART component consist multidrop parity settings. Therefore it seems convenient to replace one line with:

setReg8(UIMR1, 0x00U);

/* UMR11: RXRTS=0,RXIRQ=0,ERR=0,PM=3,PT=1,BC=3 multidrop addressable*/

,which consist PM and PT bits. I believe it need be only done initially. After I can use other UART_Serial component parts. It could be good to components update. If it works it should be straight applicable to MCF5282 chip as well.

Regards,

Marceli

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Marceli,

Thank you for the feedback and let us know the result.

best regards,

Mike

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Mike,

Thanks for legacy UART sample code for evaluation MCF5213 board. Importer classic (legacy) *.mcp project code never is working in CodeWarrior 11.1 (not seeing tooling), therefore I am always create from scratch new project using header and source files (and forget here Processor Expert components' ideas).

Hope using sample I can finally establish communication with node network devices, which using multidrop parities.

Regards,

Marceli

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

What are the other RS485 devices do you have on the bus? Are they all Freescale CPUs? I ask because "Multidrop" means a lot more than just that "parity setting". That just allows the parity bit" to be used to discriminate address and data in one (of many) possible multidrop protocols. You also need careful control of receiving, transmitting and the transmit-enable pin on the RS485 Transceiver chip for it to all work. Together with whatever "higher level protocol" is in use. Good luck.

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Here, I working with RS485 to communicate with Microchip PIC18F6720. In the chip RM datasheet (Table 21-3) description is Multidrop parity Address character or Data character type, which can be selected by PEx for use UART initial component. Does switching between both for address byte and data bytes need be done, or need to switch into Low parity type?

Marceli

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I don't know how it works.

Read Section "23.4.4 Multidrop Mode" of the User Manual. It gives a pretty good description of how you're meant to use the hardware the achieve the transmission and reception.

I suggest you also download the PIC18F6720 Data Sheet and read the USART section, specifically "18.2.3 Setting up 9-Bit Mode With Address Detect".

Reading both of those together (as they're the opposite ends of the same comms link) should give you enough information to work out how to use it.

It looks like your software does have to receive the "Address Byte" (in an interrupt routine), determine if "this device is addressed" and then switch to receiving the data if so. The whole protocol is an "efficiency hack" so that all devices don't have to spend time (and maybe battery power) receiving all data bytes. You could probably receive all data bytes and handle the protocol in software if you wanted.

Tom