- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for QorIQ

- :

- modifying the SRAM _init.tcl file

modifying the SRAM _init.tcl file

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all ,

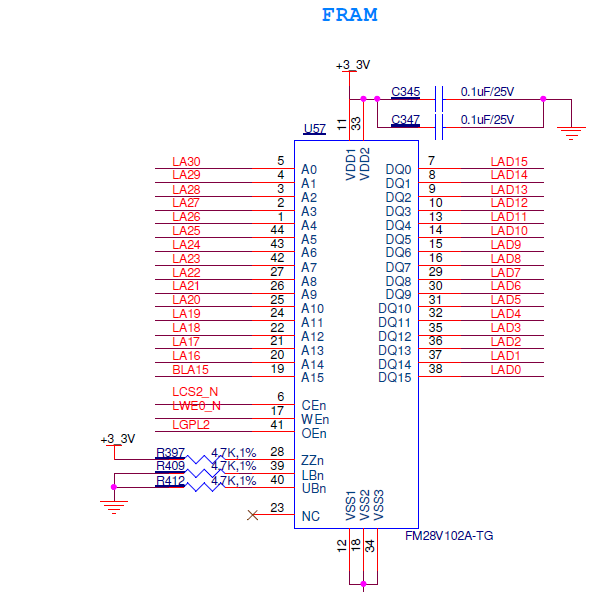

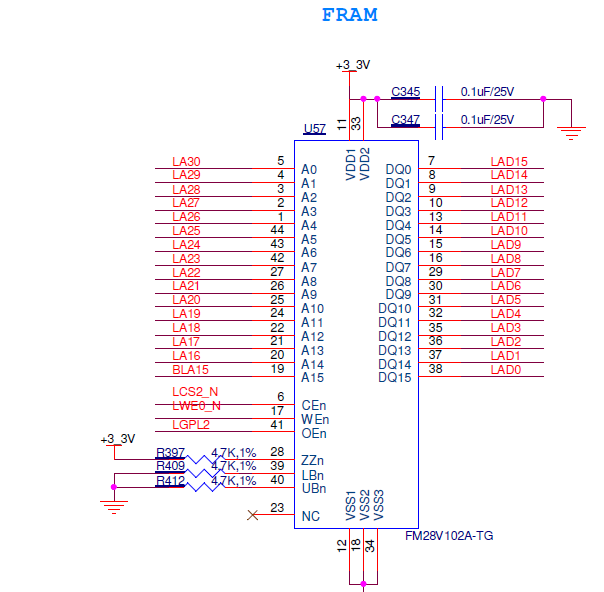

How to modify the sram _init file of P2041 for adding a FRAM connected to CS2 of p2041 in the hardware

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello agxin j,

You'll need to add this part for CS2 into eLBC controller setup section, you could refer to and edit base on the part for CS0:

# eLBC_BR0

mem [CCSR 0x124000] = 0xe8001001

# eLBC_ORg0

mem [CCSR 0x124004] = 0xf8000f85

eLBC_BR1 is for setting base address, port size, machine select and so on. Change the CCSR address from 0x124000 to 0x124008.

eLBC_ORg1 is mainly for setting address mask. Change the CCSR address from 0x124004 to 0x12400C.

Both the two registers are defined in chip reference manual, refer it for details field descriptions.

And add the part for the memory on CS2 in the LAW setup section, refer to and edit base on the part for CS0:

| mem [CCSR 0xc00] = 0x00000000 |

mem [CCSR 0xc04] = 0xE0000000

mem [CCSR 0xc08] = 0x81f0001b

This is for the memory map of the adding memory. Change the CCSR address to be the windows registers chosen, 0xCn0, 0xCn4, 0xCn8. The three registers could also be found in chip reference manual, refer to Section 2.4.

Finally add the MMU initialization for it, also refer to and edit base on the part for CS0:

reg ${CAM_GROUP}L2MMU_CAM2 = 0x9000000A1C080000E0000000E0000001Detail description of this register is contained in doc Targeting_PA_Processors.pdf, the doc is located in: D:\Freescale\CW_PA_v10.5.0\PA\Help\PDF

Have a great day,

Lunmin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello agxin j,

You'll need to add this part for CS2 into eLBC controller setup section, you could refer to and edit base on the part for CS0:

# eLBC_BR0

mem [CCSR 0x124000] = 0xe8001001

# eLBC_ORg0

mem [CCSR 0x124004] = 0xf8000f85

eLBC_BR1 is for setting base address, port size, machine select and so on. Change the CCSR address from 0x124000 to 0x124008.

eLBC_ORg1 is mainly for setting address mask. Change the CCSR address from 0x124004 to 0x12400C.

Both the two registers are defined in chip reference manual, refer it for details field descriptions.

And add the part for the memory on CS2 in the LAW setup section, refer to and edit base on the part for CS0:

| mem [CCSR 0xc00] = 0x00000000 |

mem [CCSR 0xc04] = 0xE0000000

mem [CCSR 0xc08] = 0x81f0001b

This is for the memory map of the adding memory. Change the CCSR address to be the windows registers chosen, 0xCn0, 0xCn4, 0xCn8. The three registers could also be found in chip reference manual, refer to Section 2.4.

Finally add the MMU initialization for it, also refer to and edit base on the part for CS0:

reg ${CAM_GROUP}L2MMU_CAM2 = 0x9000000A1C080000E0000000E0000001Detail description of this register is contained in doc Targeting_PA_Processors.pdf, the doc is located in: D:\Freescale\CW_PA_v10.5.0\PA\Help\PDF

Have a great day,

Lunmin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------