- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- 8-bit Microcontrollers

- :

- Consume of microcontroller

Consume of microcontroller

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I need of a microcontroller that is low-power. I found the MC9S08QA4 and i saw the que if busclock operate in the 1MHZ consumption is 490uA. This busclock Interferes where? If I put this clock frequency, time of each instruction is how much?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

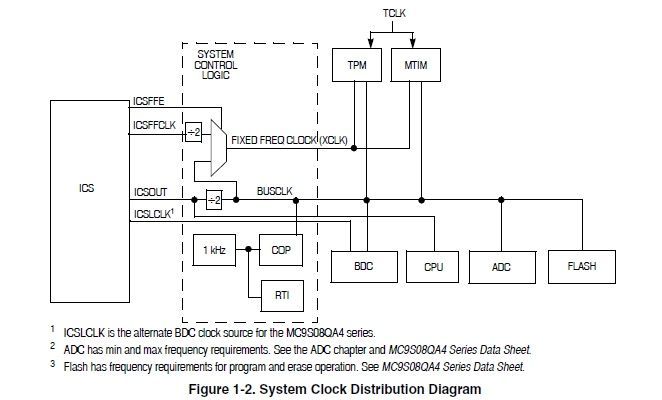

Hi Felipe, there is a system clock distrubution diagram in the reference mansule, page 19, Figure 1-2.(I inserted it below)

It shows BUCLK is coming from ICSOUT divided by 2. CPU clock is equal to ICSOUT.

That means BUSCLK = CPU CLK/2.

The instruction execution time is 1/BUSCLK. if BUSCLK is 1MHz, the time is 1us.

Hope those info can be helpfu.

B.R

Weiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Felipe, there is a system clock distrubution diagram in the reference mansule, page 19, Figure 1-2.(I inserted it below)

It shows BUCLK is coming from ICSOUT divided by 2. CPU clock is equal to ICSOUT.

That means BUSCLK = CPU CLK/2.

The instruction execution time is 1/BUSCLK. if BUSCLK is 1MHz, the time is 1us.

Hope those info can be helpfu.

B.R

Weiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I need down the bus clock, then i saw in ICS control register the ICSC2_BDIV, this register considers the main clock(20MHZ)? Then, if i want the down bus clock and put in register 10 I will have the bus clock of 5MHZ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Felipe,

From looking at the ref manual I think the value b10 will enable you to have a bus clock of 5MHz.

It's also possible you'll need to use b11 (divide by 8) as it says it divides down the clock source set by the CLKS bits!? That would mean 40MHz / 8 = 5MHz.

Regards,

Ian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Felipe and Ian,

To further clarify, the actual bus frequency will be dependent on the trim setting for the internal reference, which has a trim range of 31.25 to 39.06 kHz. The DCO frequency will be 512 times this value, i.e. 16 - 20 MHz. The bus frequency will then be determined by the BDIV factor and the additional divide-by-2 stage, as previously noted. So the following bus frequency ranges would apply.

BDIV Bus frequency range:

00 8 - 10 MHz

01 4 - 5 MHz

10 2 - 2.5 MHz

11 1 - 1.25 MHz

To achieve a bus frequency of 5.0 MHz would require a BDIV setting of 01, and a reference trim frequency of 39.06 kHz. Trimming is essential for most applications as the internal reference has a very wide tolerance (37kHz +/-25%). The trim calibration process is normally done when the code is programmed. Note that the default (and factory programmed) trim frequency for this device is actually 31.25 kHz, so would need to be altered.

The trim calibration setting will be stored in flash memory at address 0xFFAF for main trim value, and 0xFFAE for fine trim bit. The application code wll need to transfer these to the corresponding ICS registers.

Regards,

Mac

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks, i got it

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Felipe,

I could be wrong here but my understanding is that the bus clock runs at half the main clock and therefore the main clock will be running at 2MHz. The time for each instruction should be 1 / 1MHz (bus clock), which is 1us.

Regards,

Ian