- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Processors

- :

- i.MX Processors Knowledge Base

- :

- iMX6QD How to Add 24-bit LVDS Support in Android

iMX6QD How to Add 24-bit LVDS Support in Android

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

iMX6QD How to Add 24-bit LVDS Support in Android

iMX6QD How to Add 24-bit LVDS Support in Android

Introduction

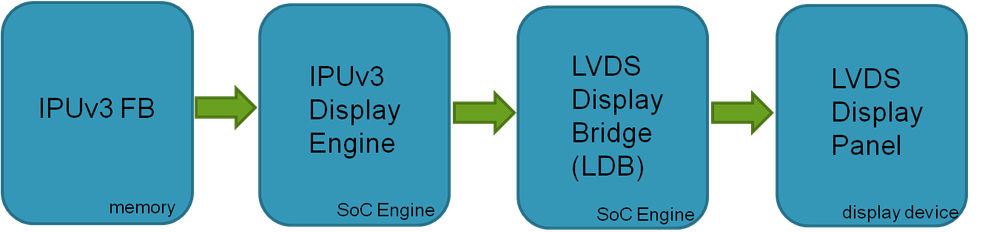

LVDS display panel driving data flow:

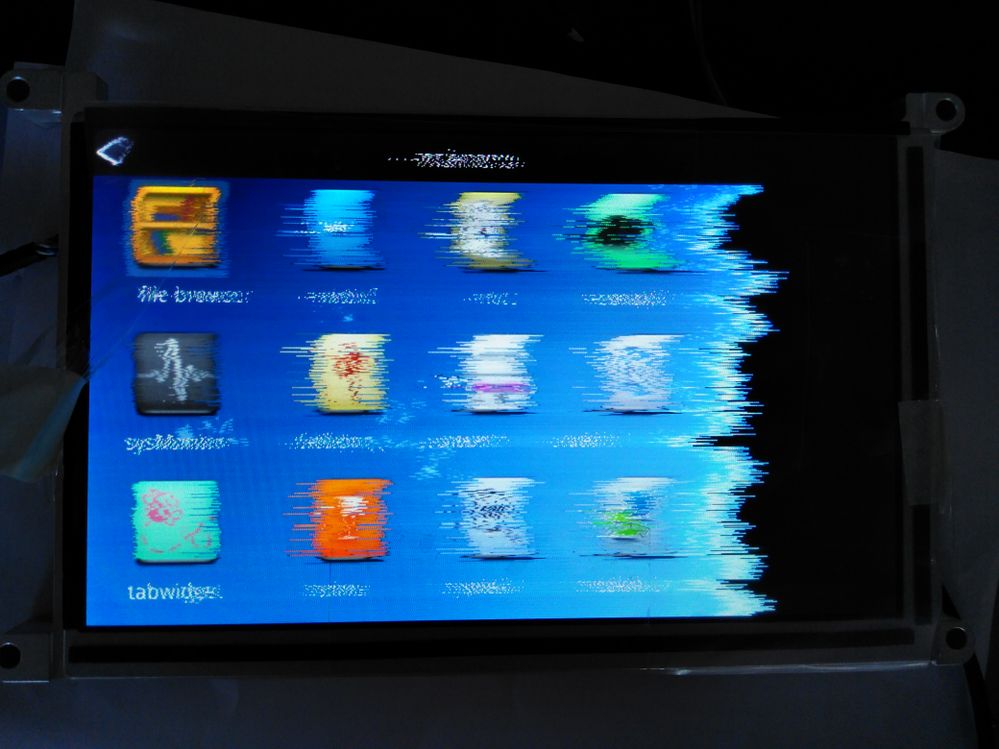

Display quality:

To get the best display quality for 24bit LVDS display panel in Android, we should use 32bit framebuffer, make IPUv3 display Engine and LDB output 24bit pixels, since RGB component information is aligned from source to destination.

2 stages to enable display:

Uboot splash screen and Kernel framebuffer

Guidelines

Uboot splash screen:

Change should be done in board file, like board/freescale/mx6q_sabresd/mx6q_sabresd.c:

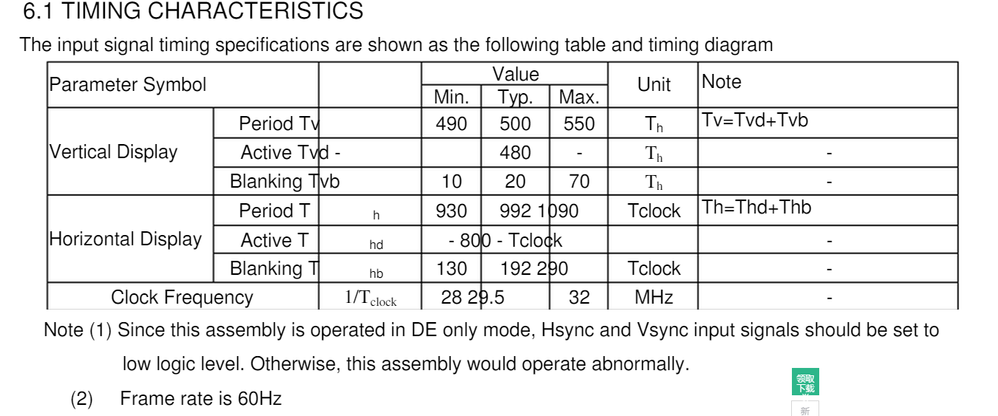

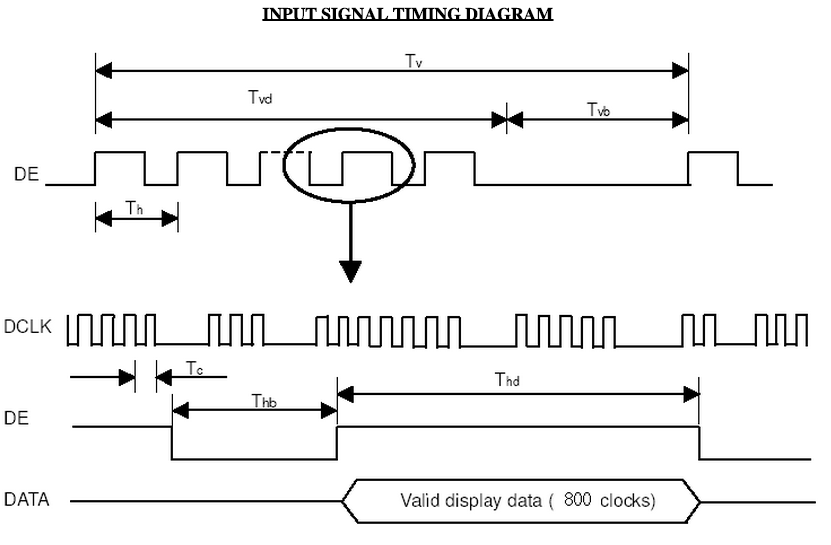

1. Set video mode in struct fb_videomode according to the new 24bit LVDS display panel’s spec(please, refer to the example at the end of this doc).

2. Set up pwm, iomux/display related clock trees in lcd_enable(). Note that these should be aligned with Kernel settings to support smooth UI transition

from Uboot splash screen to Kernel framebuffer.

3. Set the output pixel format of IPUv3 display engine and LDB to IPU_PIX_FMT_RGB24 when calling ipuv3_fb_init().

4. Set pixel clock according to the new 24bit LVDS display panel’s spec when calling ipuv3_fb_init().

5. If dual LDB channels are needed to support tough display video mode(high resolution or high pixel clock frequency), we need to enable both of the two LDB

channels and set LDB to work at split mode. LDB_CTRL register should be set accordingly in lcd_enable().

Kernel framebuffer:

As we may add ‘video=‘ and ‘ldb=’ options in kernel bootup command line, Kernel code is more flexible to handle different LVDS display panels with various display color depth than Uboot code. For detail description of ‘video=’ and ‘ldb=’ option, please refer to MXC Linux BSP release notes and Android User Guide. Some known points are:

1. Add a video mode in struct fb_videomode in drivers/video/mxc/ldb.c according to the new 24bit LVDS display panel’s spec(please, refer to the example at

the end of this doc).

2. Set up pwm backlight/display related iomux in platform code.

3. Set appropriate ‘video=‘ option in kernel bootup command line, for example:

video=mxcfb0:dev=ldb,LDB-NEW,if=RGB24,fbpix=RGB32

4. Set appropriate ‘ldb=‘ option in kernel bootup command line if dual LDB channels are needed to support tough display video mode, for example:

ldb=spl0 (IPUv3 DI0 is used) or ldb=spl1 (IPUv3 DI1 is used)

5. Set appropriate ‘fbmem=‘ option in kernel bootup command line to reserve enough memory for framebuffer. For example, if we use 1280x800 LVDS panel

for fb0 and fb0 is in RGB32 pixel format, then ‘fbmem=12M’ should be used, since the formula is:

fbmem= width*height*3(triple buf)*Bytes_per_pixel= 1280*800*3*4B=12MB

An Example to Set struct fb_videomode:

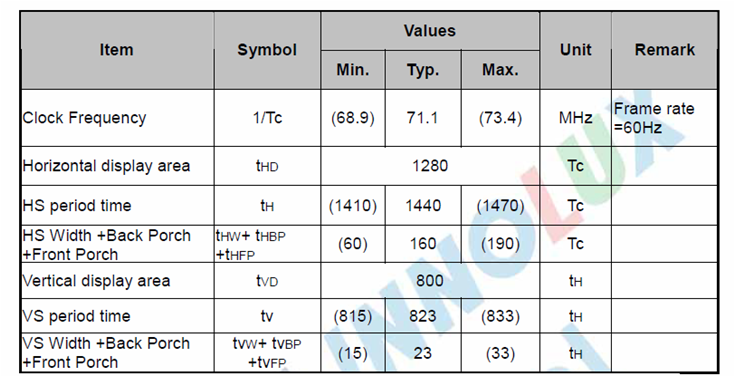

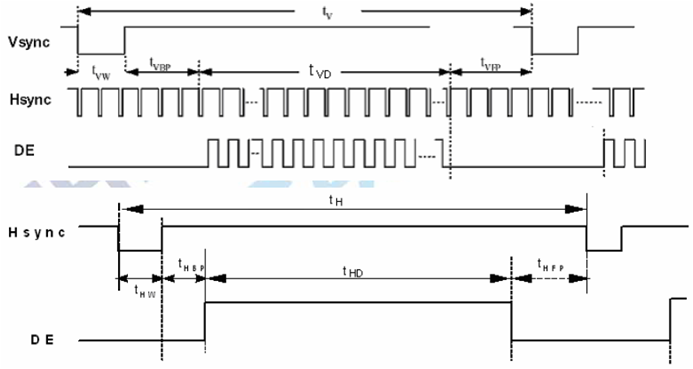

Let’s take a look at the timing description quoted from a real 1280x800@60 24bit LVDS panel spec:

And, standard linux struct fb_videomode definition in include/linux/fb.h:

struct fb_videomode {

const char *name; /* optional */

u32 refresh; /* optional */

u32 xres;

u32 yres;

u32 pixclock;

u32 left_margin;

u32 right_margin;

u32 upper_margin;

u32 lower_margin;

u32 hsync_len;

u32 vsync_len;

u32 sync;

u32 vmode;

u32 flag;

};

What we need to do is to set every field of struct fb_videomode correctly according to the timing description of LVDS display panel’s spec:

1. name: we can set it to ‘LDB-WXGA’.

2. refresh: though it’s optional, we can set it to typical value, that is, 60(60Hz refresh rate).

3. xres: the active width, that is, 1280.

4. yres: the active height, that is, 800.

5. pixclock: calculate with this formula – pixclock=(10^12)/clk_freq. Here, typically, for this example, pixclock=(10^12)/71100000=14065.

6. left_margin/right_margin/hsync_len:

They are the same to HS Back Porch(HBP)/HS Front Porch(HFP)/HS Width(HW) in the spec. Since the spec only tells us that typically

HBP+HFP+HW=160. We may set left_margin=40, right_margin=40, hsync_len=80.

7. upper_margin/lower_margin/vsync_len:

Similar to horizontal timing, the vertical ones can be set to upper_margin=10, lower_margin=3, vsync_len=10.

8. sync: Since the timing chart tells us that hsync/vsync are active low, so we don’t need to set FB_SYNC_HOR_HIGH_ACT or

FB_SYNC_VERT_HIGH_ACT. Moreover, clock polarity and data polarity are invalid, so we set sync to be zero here.

9. vmode: this is a progressive video mode, so set vmode to FB_VMODE_NONINTERLACED.

10. flag: the video mode is provided by driver, so set flag to FB_MODE_IS_DETAILED.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi There,

Thanks for this detailed guide, very helpful!

However I can't seem to see any changes to my pixel clock, can you please elaborate on your u-boot step #4 " 4. Set pixel clock according to the new 24bit LVDS display panel’s spec when calling ipuv3_fb_init()."

How is this actually done? Which file should we be modifying in u-boot. Anything we change it always seems to output 75MHz. We are using the mainline u-boot 2014-10 source.

Thanks,

Patrick

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Thank you for the tutorial. But as i see, it is not applicable in Android Lollipop release, because the "ldb.c" is different.

In my case the timings are fine. I have a LVDS panel that does not support EDID. I just want to change the default resolution from 1024x768 to 1024x600. My lvds panel works fine but the bottom stays outside of the panel. How can i fix this in Android Lollipop?

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

LCD:CHIMEI G070Y2-L01

MCU:IMX6D

{“LBD-CHIMEI”,60,800,480,33898,

190,0,

14,14,

2,2,

0,

FB_VMODE_NONINTERLACED,

BF_MODE_IS_DETAILED,

}

LCD AA084BX01 works fine

please help

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

I have found the problem,it seems pixclock can only be set to up 40MHz,lower then 40MHz it's always output 40MHz,and my lcd can only works in 27MHz to 32Mhz