- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- ls1021a unable to disable SERDES module with RCW

ls1021a unable to disable SERDES module with RCW

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi everyone,

i m facing problemes with a microcontroler based on ls1021a (it is the tqmls1021a-cc). We are trying to disable the SERDES module with the RCW using the ref manual. section 32.1.1.1.2.1 procedure.

PBL preamble and RCW header

aa55aa55 01ee0100

0 32 64 92

0608000a 00000000 00000000 00000000

128 160 192 224

FF000000 00C07900 40025a00 21046000 (boot failures)

07000000 00007900 40025a00 21046000 ( with this configuration we boot. With any other one we don't)

256 288 320 352

00000000 00000000 00000000 000bc800

384 416 448 480 512

20124900 0004b340 00000000 00000000

Are we missing something in the procedure to disable the serdes module properly ?

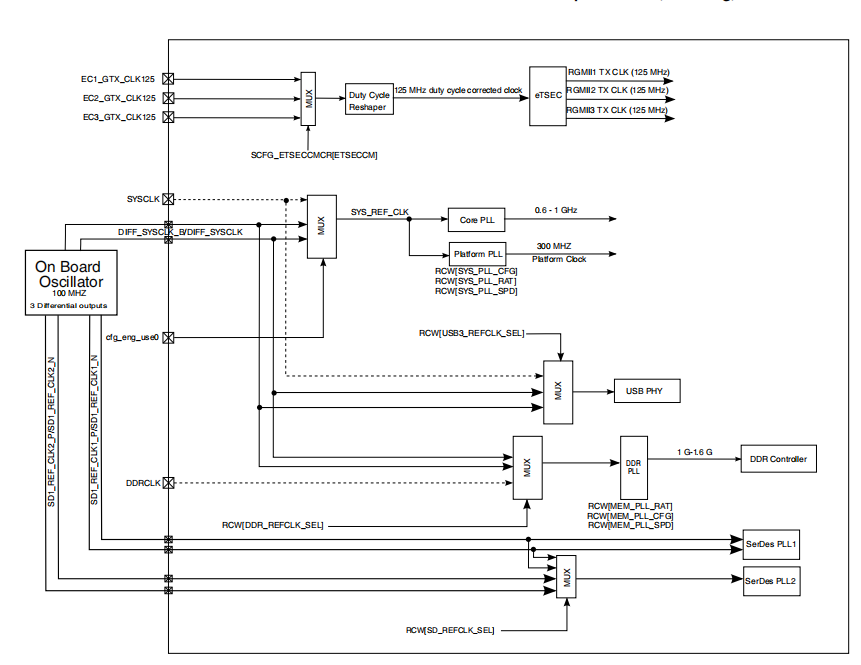

We would like to use etsec2 has RGMII. But we think that the SERDES module initialize some register during power on reset to force the controller to be in SGMII. this is why we need to be able to turn the SERDES module off.

We are basing our hypotesis on this from the refenrence manual :

20.5.8 Ethernet control register (eTSECx_ECNTRL)

ECNTRL is a register writable by the user to configure and initialize the eTSEC. Note

that the FIFM, GMIIM, TBIM, RMM, and RPM fields are read-only, having been set

after sampling signals at power-on-reset

and also on the SERDES protocole documentation.

So far we don't know yet if its possbile to configure etsec2 properly for RGMII mode with the SERDES module powered on.

We are using QCVS to generate RCW.

thank you for your support.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) I could check RCW if it will be provided as binary image.

2) To configure the eTSEC2 into RGMII mode it is required to select RCW[EC2]=000 (RGMII2).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ufedor,

We found our problem, it was related to our pbi. For a while i was investigating only on the RCW side. At some point i went to check the pbi and a mistake was made. There was a PBI command (09ea00e4 10000000) that was writing to the SERDES modules and explained the undifined behavior we encountered about RGMII for etsec2.

Thank you for your support.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I found the same problem about RCW,when writed “FF”or“C”in the RCW control word to disable the SerDes module, ls1020A boot failure.

FF000000 00C07900 40025a00 21046000 (boot failures).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please create new thread if you did not implement the mentioned PBI command.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the update.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SerDes PLL1 and PLL2 connect to GND,the ls1020 boot failure.

or

set the RCW control word like this,1020 boot failure too.

#PBL preamble and RCW header

aa55aa55 01ee0100

#enable IFC, disable QSPI and DSPI

0608000c 00000000 00000000 00000000

FF000000 08C08028 60040a00 81046000

00000000 00000000 00000000 0002a800

80000100 0004b548 00000000 00000000

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) I could check RCW if it will be provided as binary image.

2) To configure the eTSEC2 into RGMII mode it is required to select RCW[EC2]=000 (RGMII2).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ufedor,

thanks for your reply,

The yellow field correspond to etsec 1,2 and 3 configurations (they are already set to 000 wich is RGMII).

The green one concerns the SERDES fields.

this is our current RCW wich we can boot on properly :

0 32 64 92

0608000a 00000000 00000000 00000000

128 160 192 224

70000000 00007900 40025a00 21046000

256 288 320 352

00000000 00000000 00000000 000bc800

384 416 448 480 512

20124900 0004b340 00000000 00000000

If the byte 128 value is 0x70, our module boots. But any try to change the SERDES mode leads to boot failures.

We are using QCVS to build our RCW.

I attached to my reply our RCW binary generated with QCVS corresponding to our configuration that boots. (RCW_PBL.bin)

And our test with our RCW with the SERDES module off that does not boot based on the steps described in the ls1021a ref manual (32.1.1.1.2.1 Disabling unused SerDes modules) . To enable the generation of this RCW under QVCS, we had to unable the option "Enabling Ignore Constraints and non-Critical Errors option" (RCW_SERDES_OFF.bin)

thank you for your support.

Regards.