- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- S9KEAZN8AMFK Exposed Pad Connection Problems

S9KEAZN8AMFK Exposed Pad Connection Problems

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am use FRDM-KEAZ128Q80 as OpenOCD debugger, and it works well on a S9KEAZ128AMLH chip. but when I try to debug a S9KEAZN8AMFK mcu ,It doesn't work. It can't reconize the mcu.

I have connected the Exposed Pad to the ground, I searched the <KEA8 Sub-Family Reference Manual> but I don't found how to deal with the Exposed Pad.

My schematic has been attached. *Note that I have been conncted the Exposed Pad to the ground.

I tested the pin PTA5/RESET voltage is 2.8v , it is very strange. help me please .

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ZhongYao,

The RESET_b pin, if enabled, must have a 100 nF capacitor close to the MCU for transient protection. The NMI_b pin, if enabled, must not have any capacitance connected to it. Each pin, when enabled as their default function, has a weak internal pullup, but an external 4.7 kΩ to 10 kΩ pullup is recommended.

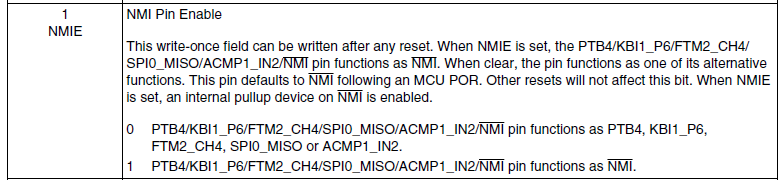

After reset, the shared peripheral functions are disabled so that the pins are controlled by the parallel I/O except PTA4, PTA0, PTB4 and PTA5 that are default to SWD_DIO, SWD_CLK, NMI and RESET function. Driving the NMI signal low forces a non-maskable interrupt, if the NMI function is selected on the corresponding pin.

If you hope the PTB4(deault as NMI_b function) as SPI0_MISO, please modify the NMIE bit in SIM_SOPT register first.

I think you can configure PTB1 as SPI0_MISO function instead of using PTB4(NMI_b).

Then configure PTA3 as UART0_TX and PTA2 as UART0_RX. (Please note that PTA2 and PTA3 are true open-drain pins when operated as output.)

If you want use the debugger on FRDM-KEAZ128, please isolate the on-board MCU from the debug interface. (for example don't use the R101)

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks to Robin, problems has been solved. These problems cased by NMI_b pin connection, I cut the NMI_b wire on my pcb then it could be recognized by J-Link. Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ZhongYao,

The RESET_b pin, if enabled, must have a 100 nF capacitor close to the MCU for transient protection. The NMI_b pin, if enabled, must not have any capacitance connected to it. Each pin, when enabled as their default function, has a weak internal pullup, but an external 4.7 kΩ to 10 kΩ pullup is recommended.

After reset, the shared peripheral functions are disabled so that the pins are controlled by the parallel I/O except PTA4, PTA0, PTB4 and PTA5 that are default to SWD_DIO, SWD_CLK, NMI and RESET function. Driving the NMI signal low forces a non-maskable interrupt, if the NMI function is selected on the corresponding pin.

If you hope the PTB4(deault as NMI_b function) as SPI0_MISO, please modify the NMIE bit in SIM_SOPT register first.

I think you can configure PTB1 as SPI0_MISO function instead of using PTB4(NMI_b).

Then configure PTA3 as UART0_TX and PTA2 as UART0_RX. (Please note that PTA2 and PTA3 are true open-drain pins when operated as output.)

If you want use the debugger on FRDM-KEAZ128, please isolate the on-board MCU from the debug interface. (for example don't use the R101)

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin

I made an automotive product using S9KEAZN8AMFK.

I know that S9KEAZN8AMFK is AEC-Q100 Grade 1.

And the company we supply products to says they need an AEC-Q100 Grade 1 certification test report.

I must submit proof that S9KEAZN8AMFK is AEC-Q100 Grade 1.

Can you send me the AEC-Q100 Grade 1 certification test report?

Best Regards,

romeo