- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Software Development Kit

- :

- LLS and Watchdog

LLS and Watchdog

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I´m making some tests and as I can see looks like watchdog stop to run when I enter in LLS mode.

Is that right or I´m doing something wrong?

my configuration is

const wdog_config_t watchdog1_InitConfig0 = { .wdogEnable = true, .clksrc=kWdogLpoClkSrc, .prescaler = kWdogClkPrescalerDivide1, .workMode.kWdogEnableInWaitMode = true, .workMode.kWdogEnableInStopMode = true, .workMode.kWdogEnableInDebugMode = false, .updateEnable = true, .intEnable = false, .winEnable = false, .windowValue = 0U, .timeoutValue = 2048U, };

thanks

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Vioder,

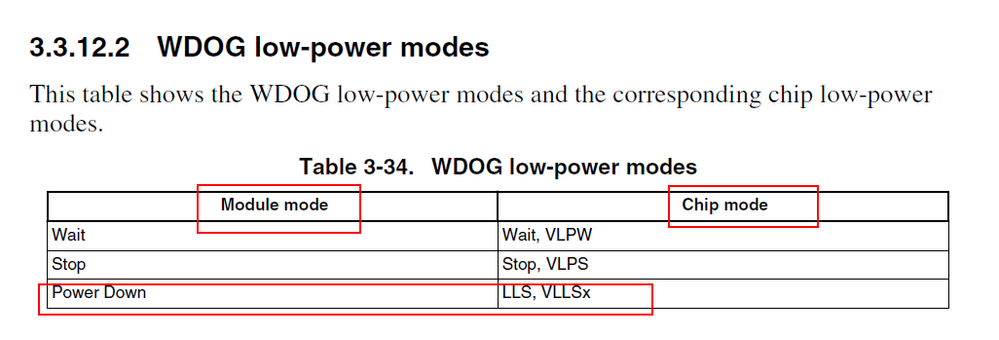

No, when the K64 chip in LLS mode , the WDOG will not work .

Please see here at your RM:

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

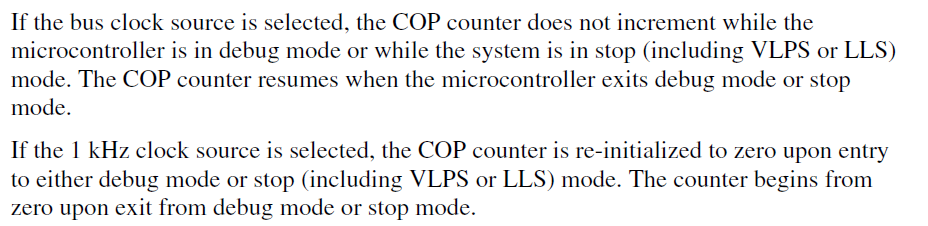

Hello Voider,

Yes , you are right ,

the COP counter does not increment while the

microcontroller is in debug mode or while the system is in stop (including VLPS or LLS)

mode.

Which chip do you used ?

You can check the Reference manual of your chip , for example the chip of KL25 ,

from the reference manual , the part of this :

3.4.10 Computer Operating Properly (COP) Watchdog

Configuration

Hope it helps

Have a great day,

Alice Yang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your quick reply.

I´m using K64 processor and the manual where I´m trying to find some information is:

Document Number: K64P144M120SF5RM Rev. 2, January 2014

The information that I found is that I can use LPO and LPO stay active in LLS mode, so I think watchdog will stay active also.

And In 24.3.36 says that watchdog still run in stop but take twice as expected time to fire.

5.7.1 PMC 1-kHz LPO clock

The Power Management Controller (PMC) generates a 1-kHz clock that is enabled in all

modes of operation, including all low power modes. This 1-kHz source is commonly

referred to as LPO clock or 1-kHz LPO clock.

Table 7-2. Module operation in low power modes (continued)

Modules Stop VLPR VLPW VLPS LLS VLLSx

1kHz LPO ON ON ON ON ON ON in VLLS1/2/3, OFF in VLLS0

24.3.6 Low-power modes of operation

Stop Where the bus clock is gated, the WDOG can run only on low-power oscillator clock

(CLK_SRC=0) if it is enabled in stop (STOP_EN=1). In this case, the WDOG runs to time-out

twice, and then generates a reset from its backup circuitry. Therefore, if you program the

watchdog to time-out after 100 ms and then enter such a stop mode, the reset will occur after

200 ms. Also, in this case, no interrupt will be generated irrespective of the value of

IRQ_RST_EN bit. After WDOG reset, the WDOG reset counter will also not increment.

I do not found anything about LLS.

Do you think watchdog in K64 will not work in LLS like KL25 ?

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Vioder,

No, when the K64 chip in LLS mode , the WDOG will not work .

Please see here at your RM:

Hope it helps

Alice