- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- iMXRT1052 and emwin planning SDRAM region with D Cache

iMXRT1052 and emwin planning SDRAM region with D Cache

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMXRT1052 and emwin planning SDRAM region with D Cache

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I build a GUI using the emwin on the iMXRT1052, the lcd and gui buffer be placed in a cacheable region of planned SDRAM space. Actual operation result, it’s performance drop during moving actions of the GUI elements. I tried to enable the D-cache for the whole SDRAM, it’s OK. But I can’t set the whole SDRAM to CACHE, the program needs to be placed Global data placement with SDRAM, and the region set to Non-cache, Is there any other solution?

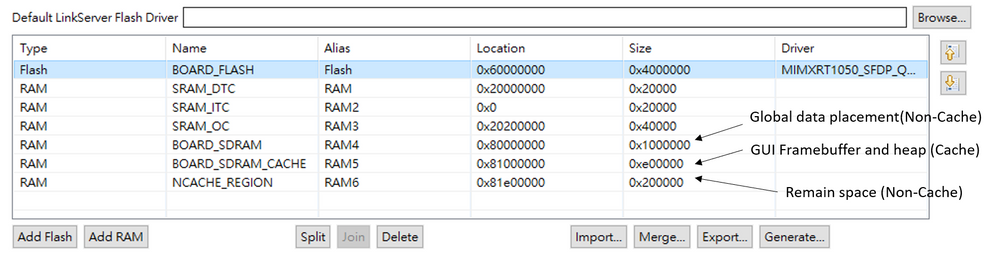

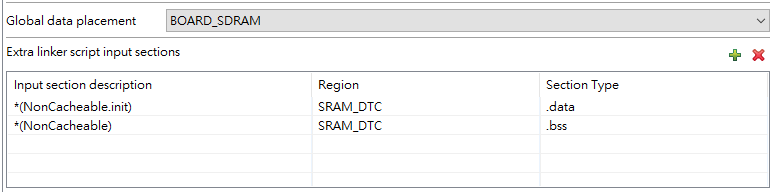

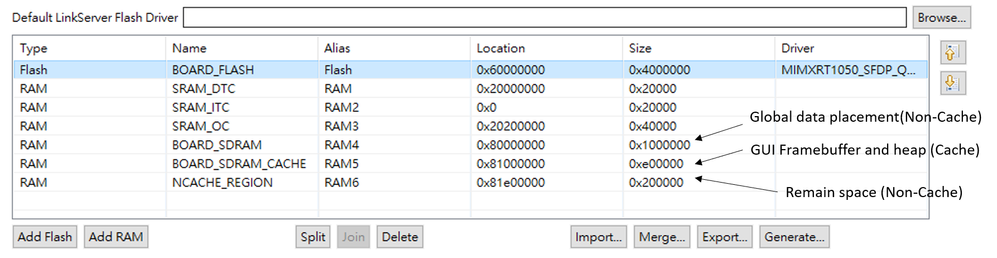

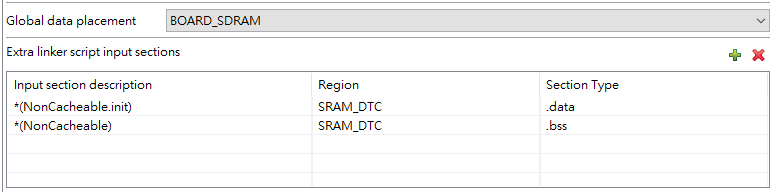

The following is memory of the system configuration.

iMX RT1050 Memory setting:

- BOARD_SDRAM: Global data region.

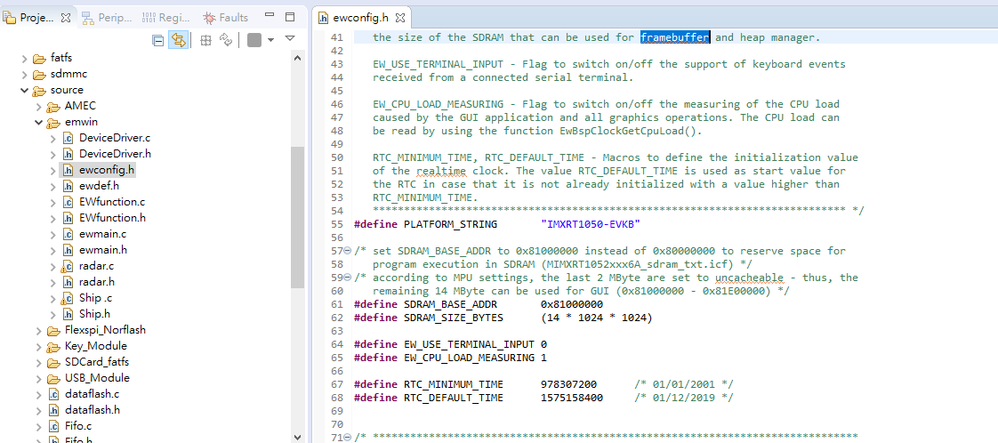

- BOARD_SDRAM_CACHE: Gui framebuffer used.

- BOARD_SDRAM_NON_CACHE: Reserved.

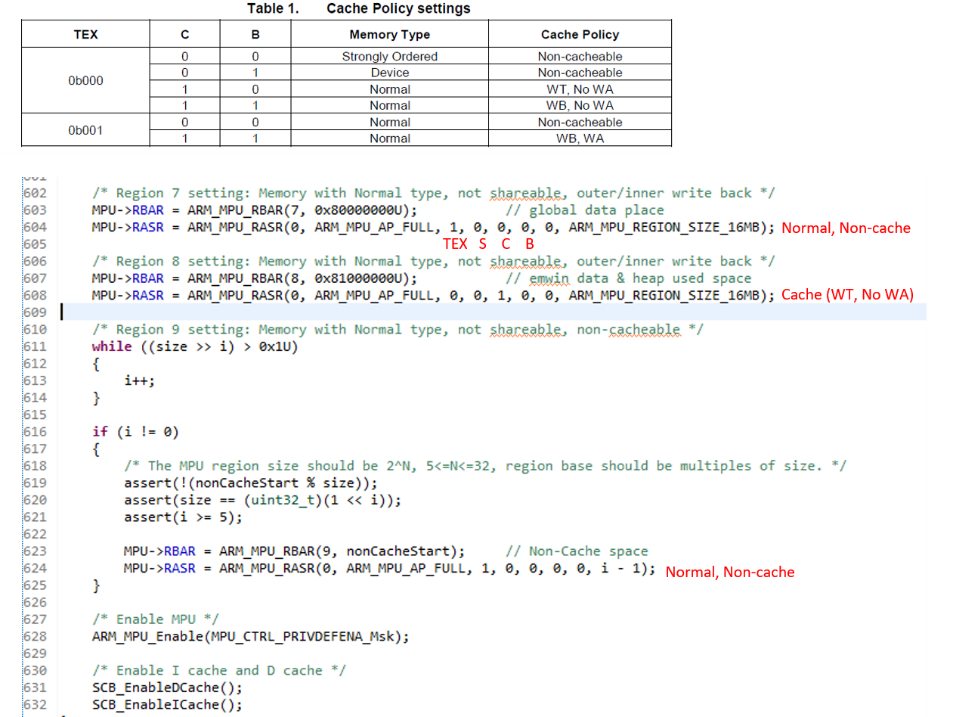

iMX RT1050 Cache setting:

GUI framebuffer mapping memory space:

Best Regards,

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

Hope you are doing well.

I believe there are some important considerations to take mentioned in the following post:

iMXRT1052 and emWin: problems with D cache

The situation is similar and may help as well. Please let me know if its answers your questions regarding what should be cached and what shouldn't.

Let me know if you have further questions.

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sabina

I tried this web link about these problem, but it's situation is different from mine, it enable the D cache for the whole SDRAM , but I divide SDRAM into tree pieces, and first pieces of SDRAM set global data placement and non-cacheable region, second pieces of SDRAM set cacheable region to provide the LCD and GUI buffers access, but this setting will cause system performance drop during moving actions of the GUI elements.

Best Regards,

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hope you are doing well.

If you divide the three sections and place non-cacheable region, it can avoid the cache data coherency problem. But the side-effect is the performance of accessing the buffer is not good as cacheable ones if CPU access them multiple times. So it is expected that the performance drops.

Maybe I misunderstood your questions, but could you please describe what is the main objective that you would like to achieve with these regions.

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------